富士通研究所は10月29日、サーバなどICT機器用のデジタル制御電源向けに開発プロセスの効率化・高信頼化が図れる開発環境を構築したと発表した。

電源の高性能化・機能高度化に伴う制御の複雑さに対応するため、ソフトウェアによる電源制御が有望視されているが、設計時のシミュレーションと実機動作とのギャップや、コーディング量の増大と、それに伴う人為ミスによるバグ混入のためデバッグ・試験工数が増大し、開発の効率化が課題となっていた。

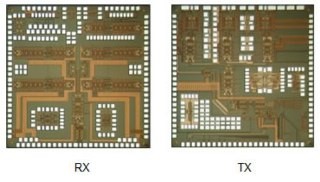

今回、電源制御に必要な最大150kHz超の速い動作の制御信号を、150ピコ秒の高い分解能でモデルどおりに生成できる高速高分解能IOボードを開発した。さらに、組み込みコード自動生成技術と組み合わせることでコーディング作業を不要にし、電源実機に対するソフト制御動作の妥当性検証とマイコンへの実装を実現する開発環境を構築した。これにより、開発工数を従来手法の約1/3にできる見込みという。

今後、同技術を適用し開発工数を削減することで、高性能ICT機器向けだけでなく、自動車の高度な電源制御など多様な電源のニーズにもタイムリーに応えることが可能になるとコメントしている。