テクトロニクス社は9月24日、次世代のモバイルメモリ技術であるJEDEC LPDDR4のPHY(物理レイヤ)および適合性のテストソリューションを発表した。

LPDDR4は2015年に導入が予定されており、現状のLPDDR3技術上に構築されている。データレートは最高4.26Gbpsで、超低電圧コアにより消費電力は約35%低減され、スマートフォンやウェアラブルデバイス、タブレット端末などのモバイルデバイスのパフォーマンスが強化されるという。

一方で、LPDDR4には入出力電圧が1.1V、および高速のデータレートとコンパクトな機械設計によりテストポイントへのアクセスが限定されるなど、新たなテスト・測定課題がある。また、Vref、リード/ライトバーストなどのさまざまな変更もあり、JESD209-4仕様で規定されているテストもさらに複雑になっている。今回、LPDDR4設計における検証用ツールとして発表された同ソリューションは、テストのセットアップ、実行の自動化により、テストサイクルに要する時間を、数週間から数時間まで短縮することができる。

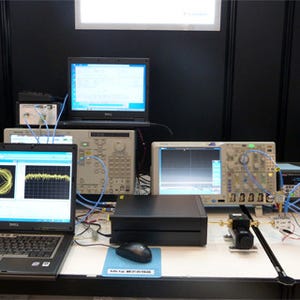

具体的には、DDR-LP4解析ソフトウェアにより、LPDDR4規格に対する統合された物理レイヤテストとデバッグが提供される。セットアップ、テストが自動化できるため、メモリ規格への適合性を確実なものにすることができる。仮にメモリシステムが適合性試験でフェイルになった場合でも、すばやくデバッグモードに切り替え、同社のオシロスコープのビジュアルトリガなどのツールでイベントを特定できる。そして、DPOJETジッタ/アイダイアグラム解析ソフトウェアにより、詳細な解析が行える。

この他、パートナ企業であるNexus Technologyと共同開発したLPDDR4用メモリコンポーネントインターポーザ「EdgeProbe」も合わせて発表した。同製品は、モバイル設計に求められる厳しい機械的条件で設計されており、ソケット型インターポーザによって、操作性、再利用性、コンポーネントの交換性に優れているとしている。