「High Bandwidth Memory(HBM)」は、TSV(Through Silicon Via)技術を使いメモリチップから多数の信号線を引き出し、高バンド幅のDRAMモジュールを作るという技術で、メモリ関係の標準化を担当してきたJEDECで標準化が行われている。

一方、ThruChipの技術は、慶応義塾大学(慶応大)の黒田教授のグループが開発してきた3D実装されたチップ間を磁気結合で信号伝送するという技術で、積層されたチップ間をTSVで繋ぐより低コストで3D実装ができるのが売りである。ただし、JEDECのような強力な標準化団体が、この技術の採用には動いていないので、今後、支持を広げられるかどうかが鍵である。

DRAMチップは多数のメモリアレイを集積しており、それぞれのアレイから数千ビットを並列に読み出すことができる。従って、チップ自体は非常に大きなバンド幅を持っているのであるが、チップがx4とかx8、GDDRでもx32と入出力ピン数が制限されているため、DRAMチップのバンド幅を大幅に改善することができない状態になっている。

これに対して、DRAMチップから1024信号を引き出し、各信号線で1Gbit/sの伝送を行えば1Tbit/sという高バンド幅のメモリが作れることになる。しかし、現在使われている実装技術では、このように多くの信号線を引き出すことはできない。

そこで出てきたのが、シリコンチップに穴を開け、プリント板のビアのように、表裏を接続するTSVを作るという方法である。TSVのピッチは50μm程度と小さいので、それほど大きな面積を使わなくても1024信号を引き出せる。

HBMでは1024信号をTSV技術でメモリチップのスタックから引き出し、インタポーザなどの高密度の接続で、これをCPUチップに接続するという形態を想定している。この配線は短く寄生容量Cが小さくCV2fが小さく、消費電力も減るというメリットがある。

一方、黒田先生考案の近距離磁気結合方式は、積層したチップ上に位置を合わせたコイルを作り、このコイル間を磁界で情報を伝達するという技術で、100μm角のコイルで8Gbit/sの伝送ができ、信号の伝送ではTSVによる接続に負けないという。しかし、信号は磁気結合で行けるとしても、チップ間の電源やグランドの接続が問題になる。これについては、ThruChipは極薄チップの製造と高ドープのシリコンで十分低抵抗の接続が可能としている。

SK HynixのHBM

Hot Chips 26において、SK HynixのJoonyoug Kim氏とYounsu Kim氏がHBMについての発表を行った。

プロセサやGPUなどの性能向上に伴って、DRAMのバンド幅の改善が求められている。しかし、DIMMなどの形で供給されるDRAMではプロセサのバンド幅の要求に追いついていない。DIMMは信号線が64本であり、1.6Gbit/sで伝送しても12.8GB/sのバンド幅である。これに対してHBMは1024本の信号線を持ち、1~2Gbit/sで伝送するので、最大256GB/sと桁違いに高いバンド幅を実現することができる。

携帯機器の小型化に伴い、パッケージの小型化が求められ、次の図の左側の写真のように、複数枚のDRAMチップをずらせて重ね、金線のワイヤボンドで接続したものが使われているが、右側の写真のように、複数枚のDRAMチップをTSVで積層するHBMを使えば、パッケージのサイズは36%になり、128GB/sのバンド幅を得るのに必要な実装面積は、11%で済む。また、消費電力も51%と半減できる

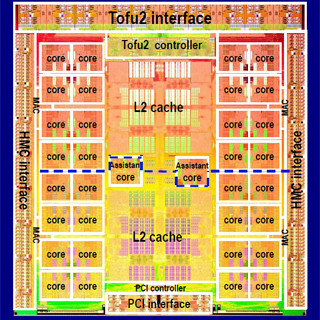

HBMの規格では、4枚のDRAMチップと、1枚のベースロジックチップをTSVで接続する。それぞれのDRAMチップは2つのチャネルに分けられており、各チャネルから128本のI/Oが出ている。従って、4枚のDRAMチップには合計8チャネルがあり、合計1024本のI/Oが出ている。これら全てのI/OはTSVで引き出され、一番下のロジックチップに接続される。

HBMに使われるDRAMチップにも改良が施されている。各チャネルは8バンクに分かれており、バンクごとにリフレッシュを行うことができるようになっており、リフレッシュ中も、他のバンクは通常のアクセスができるようになっている。また、HBMではRASとCASのアドレス線が分離されたデュアルコマンドとなっており、1つのコマンドの終了を待つことなく、オーバラップして次のコマンドを発行できるようになっており、コマンド発行の効率を高めている。

HBM規格の第1世代は、2GbitのDRAMチップを使い、データ転送速度は1Gbit/sで、HBMの容量は1GB、バンド幅は128GB/sとなる。第2世代では8GbitのDRAMチップを4枚、あるいは8枚スタックし、I/Oピンのデータ転送速度も2Gbit/sに引き上げるという計画である。

現在のDDR3、グラフィック用のGDDR5とHBMの諸元を比較すると次の表のようになる。

TSVを作るための加工や、そのための歩留まり低下などから、値段が高くなるという懸念があるが、パッケージが小さく、消費電力が低いというメリットから、スマホなどの小型の携帯機器や、GDDR5を上回るバンド幅からGPUのデバイスメモリとしての使用などの多少のコストアップが許容できる用途からHBMの採用が進んでいくと思われる。