NVIDIAはGTC 2014で、次世代GPUとして、2016年に「Pascal」を出すというロードマップを発表した。

このロードマップでは、2014年に出荷の始まった「Maxwell」の次に2016年に「Pascal」を出すことになっている。しかし、昨年のロードマップでは、時期は明示されていないが、「Maxwell」の次はStacked DRAMを使う「Volta」が出ることになっている。NVIDIAの広報に「Volta」はどうなったのかと質問すると、公式のQ&Aでは、「Volta」に先行して「Pascal」を出すロードマップに変更されたということで、「Volta」は無くなったということではないとのことであった。

しかし、「Volta」も「Pascal」も「Maxwell」の2倍弱の性能/電力値の改善であり、「Volta」のStacked DRAMに「NVLink」を加えて「Pascal」と改名した感じである。

「Pascal」での一番の目玉は「NVLink」と呼ぶ、高速リンクである。現在、GPU間、あるいはCPUとGPUの間はPCI Expressで結ばれており、PCIe3.0の×16でも16GB/s×2のバンド幅である。これに対して、「NVLink」は80GB/s~200GB/sのバンド幅を持ち、PCIe3.0と比べて5倍~12倍の性能を持つというのがうたい文句である。

次の図のように、「NVLink」を使って、CPUとGPUの間をつなぐことができる。

「NVLink」で接続すると、それぞれのデバイスのメモリが共通のメモリ空間に配置され、CPUからGPUのデバイスメモリ、GPUからCPUや他のGPUのメモリをアクセスすることが可能になる。

ただし、このような接続を行うには「NVLink」に対応したCPUが必要である。NVIDIAはCPUメーカー各社に「NVLink」のサポートを呼び掛けているとのことであるが、現在のところコミットしているのはIBMのPOWERだけという。

QPIを持っているIntelやHyperTransportを持つAMDが「NVLink」をサポートするのは考えにくいので、NVIDIAの自社開発の「Denver」が独立のCPUチップになる場合や、ARMのサーバチップのメーカーがサポートするというのが考えられるケースである。

CPUに「NVLink」のサポートがない場合は、次のようにGPU間の接続として「NVLink」を使うことができる。

この場合は、CPUとの接続はPCI Expressだけになってしまうが、GPU間では共通のメモリ空間になる。

ただし、「NVLink1.0」では、キャッシュコヒーレンシの機能はなく、CUDA6のUnified Memoryと同様に、デマンドページングでページ単位で移動を行うのではないかと思われる。なお、CUDA6では、Kepler GPUの場合は、CPUからのアクセスに対しては4KiBのページ単位のデマンドページングであるが、GPU側のページは8KiBであるので、デマンドページングができず、GPUカーネルの呼び出し直前に一括転送しているのであるが、「Maxwell」ではGPU側も4KiBページをサポートし、両方向のデマンドページングができるようになっている。「Pascal」でも当然、この機能はサポートされるはずである。

「NVLink」ではDMA+をサポートしており、デマンドページングのページの転送のためなどに使用されると考えられる。なお、DMA+の"+"は何かと質問したのであるが、明確な答えは得られなかった。

物理的には「NVLink」は差動伝送で20Gbit/sで単方向のデータ伝送を行うリンクで、送受それぞれに8レーンの伝送路を持っている。2014年2月のISSCCでNVIDIAは20Gbit/sの半二重のトランシーバを発表しており、半二重と全二重の違いはあるが、同様な技術が使われていると考えられる。

20Gbit/sで各8レーンであるので、送受ともに20GB/sのバンド幅を持っている。前の図のようにGPUからは4本のリンクが出ており、全体の合計のバンド幅は160GB/sとなる。これはPCIe3.0 x16の10倍のバンド幅である。NVIDIAの言う5倍~12倍の根拠はよくわからないが、10Gbit/sにして伝送路の条件を緩めたり、伝送速度を25Gbit/sまで引き上げるようなバリエーションを作ることは考えられる。

そして、将来の「NVLink2.0」では、キャッシュライン単位のコヒーレンシをサポートし、マルチソケットのCPU間の共有メモリと同じ機能を実現する予定である。

そして、Pascalでは高バンド幅のHigh Bandwidth Memoryを採用する。

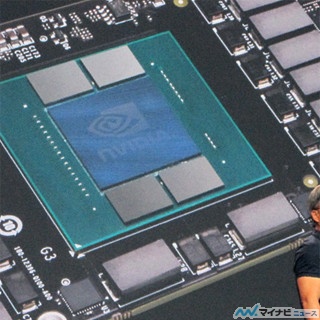

中央のパッケージが「Pascal」で、周囲に並んでいるのは、すべてVoltage Regulatorを構成する部品である。この図では、見えないが、裏側に2個のコネクタがあり、このボードはメザニンカードとしてマザーボードの上に搭載されるとのことである。

Pascalモジュールは、中央に大きなGPUチップがあり、その上下に各2個のHBMが搭載されている。

JEDECで規格策定しているHBMは、4枚、あるいは8枚のDRAMチップをTSVで積層し、1024bit幅のインタフェースで1Gbit/sでデータ転送を行うというもので、1個で128GB/sのメモリバンド幅を持っている。そして、第2世代ではデータ転送速度を2Gbit/s以上に引き上げ、バンド幅を256GB/s以上に引き上げる目論見である。現在のGDDR5メモリは、7Gbit/sのデータ転送速度を使っても28GB/sのバンド幅しかないのと比べると、HBMは圧倒的に高バンド幅である。

このようなHBMを4個使用すると、512GB/s、あるいは1TB/sのバンド幅が得られる。現在のGPUが300GB/s程度のバンド幅であるのと比べると、HBMの採用により、バンド幅を大きく向上させられる。また、消費電力もGDDR5の1/4になるという。このHBMの採用でボードサイズが現在のPCI Expressカードの1/3になり、その分、高密度実装が可能になるという。

なお、写真のPascalボードは完全なモックアップで、製品になるときにはHBMの搭載個数などは変わる可能性があるという。