Alteraは、CPLD、FPGA、SoC FPGA、HardCopy ASICデザイン向け開発ソフトウェア・スイート「Quartus II」 の最新バージョンとなる「Quartus II v12.1」をリリースしたことを発表した。

同バージョンでは、従来のハードウェア開発作業を継続的に軽減することにより、デザイン環境を強化。これにより、ユーザーは生産性の最大化を図れるようになったほか、各種FPGAなどの性能の利点を得ることができるようになったという。

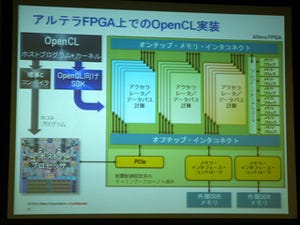

また、OpenCL向けSDKの高度なデザイン・フローもサポートしたほか、システム統合ツール「Qsys」とモデル・ベース設計環境「DSP Builder」も強化が図られている。

さらに、パーシャル・リコンフィギュレーション・デザイン・フローや、新しいIPコア、新しい28nm FPGAおよびSoCデバイスのサポートなども追加されたという。