Xilinxは7月26日(現地時間)、同社の次世代設計環境「Vivado Design Suite」の一般ユーザー向けリリースを発表した。

今回、使用可能となった「Vivado Design Suite 2012.2」は、「ISE Design Suite」ライセンスの保証期間内に該当するすべてのユーザーが追加のライセンス費用を支払うことなく使用できる。同ツールは、2つのフェーズに分けて展開されるうちの最初のリリースで、C言語およびRTLからのインプリメンテーションを加速させることにフォーカスした機能を提供している。「Vivado Design Suite 2012.2」は、高位合成や、System VerilogをサポートとしたRTL合成、分析的な配置配線、最先端SDCベースタイミングエンジンなど、全く新しいシステム-IC間ツールを備えた高度な統合設計環境(IDE:Integrated Design Environment)を提供する。このツールを活用することで、開発者はデザインのインプリメンテーションにおける生産性を最大4倍向上させることが可能になる。

今日のデザインにおけるサイズおよび複雑性が要因となり、設計時に多次元的な課題に直面し、自動デザインクロージャを実現することが難しくなっている。「Vivado Design Suite 2012.2」に採用されている配置配線技術は、密度やワイヤの全長、タイミングなど、デザインの評価に必要な値を複数かつ同時に最適化する分析技法を使用することでインプリメンテーション時間を短縮させる。複雑なデザインのケースでは、「ISE Design Suite」の場合と比較して15%の性能向上が見られ、これは1スピードグレード分のアドバンテージとなる。中間クラスのFPGAファミリでは3スピードグレード以上のアドバンテージを実現し、ハイエンドのデバイスにおいては、同等の消費電力でより高性能を実現する。さらに、プロダクトポートフォリオのうち低コストクラスのデバイスでもより高い性能を可能にする。

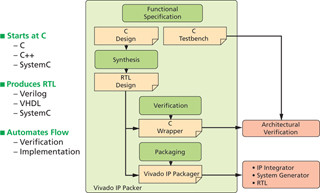

また、C、C++、SystemCコードをRTLに合成し、複雑なアルゴリズムに対応するインプリメンテーションアーキテクチャを短時間で検証することが可能になる。Vivado高位合成(HLS:High-Level Synthesis)ツールは、高速シミュレーションモデルを作成することでSystem Generatorと統合することが可能で、ビデオ、画像処理、RADAR、ベースバンド無線などのアプリケーション開発を短時間で実現する。さらに、アルゴリズムのインプリメンテーションを加速するだけでなく、RTLのマイクロアーキテクチャ検証により、検証時間を最大で1万倍高速化しながらシステム性能の向上を実現する。

同社は、さらなるデザインの生産性向上を実現するために、拡大しているザイリンクスアライアンスプログラムにおいて、その主要メンバー企業と協力し、IPコアの検証や利用可能なデザインツールを通じて「ISE Design Suite」および「Vivado Design Suite」ツールを強化している。また、「Vivado Design Suite」の2つ目のフェーズでは、Vivado IPインテグレータの提供や、インタラクティブなデザインおよび検証環境、ザイリンクス製およびサードパーティ製、カスタマイズIPコアを、制約やテストベンチ、ドキュメンテーションなど必要となるものすべてをともに利用することが容易に実現できるVivado IPパッケージャーの提供を予定しているが、これらに向けてもメンバー企業と協業を続けている。

なお、「ISE Design Suite」のライセンスが保証期間内であれば、Logic EditionおよびEmbedded Editionのユーザーは「Vivado Design Suite Edition」を、「ISE Design Suite DSP」およびSystem Editionのユーザーは「Vivado Design Suite System Edition」を追加のライセンス費用を支払うことなく利用できる。「ISE Design Suite」および「Vivado Design Suite」の最新バージョンは、同社のホームページからダウンロードできる。また、「Vivado Design Suite」のトレーニングクラスも提供されている。