Xilinxは4月24日(米国時間)、同社FPGA向け次世代デザインスイート「Vivado Design Suite」を発表した。同スイートを活用することで、従来のFPGAに加え、3Dスタックド・シリコン・インタコネクト(SSI)テクノロジやARMプロセッシングシステム、アナログ・ミクスドシグナル(AMS)などの半導体IPを組み込んだ次世代デバイスのプログラマブルシステムのインテグレーションおよびインプリメンテーションを短時間で実現することが可能になると同社では説明している。

同社日本法人ザイリンクスの代表取締役社長のサム・ローガン氏は、「Xilinxは次の10年を"All-Programabe"の時代だと言っている。プログラマブルロジックがASIC/ASSPの代わりにシステムの中心に置かれるようになってきており、それをハードウェアとしてサポートしたのが"Zynq"だ。Vivadoはそうしたハードウェアをサポートするためのツールで、ミクスドシグナルやアナログ、スイッチなどを1つのツールで管理することを目的に開発された」とその開発経緯を説明する。ちなみにVivadoの語源を同氏に聞いたところ「2つの意味を併せた造語(開発コード名はRodinとのこと)。ラテン語でVivaは"命"を表し、Vadoは"自信を持つ"というような意味で、2つを併せて"自信を持って提供するもの"といったようなニュアンスを込めている」(同)とのことであった。

|

|

|

|

システムの中心にASICやASSPの替わりにFPGAが置かれると、従来のロジックのみではなくSoC的にアナログやミクスドシグナル、I/Oなどの機能もFPGA上で実現することが求められるようになる。また、マルチダイ構成などの大規模回路における物理的な最適化なども求められるようになる |

|

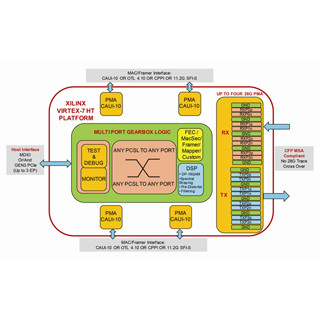

また、Virtex-7のハイエンド品などはSSIテクノロジを採用して1チップ内に4ダイを集積しており、「この場合、ダイ間のレイテンシは1μsだが、1ダイ上にすべての回路を入れた方が良いのか、複数のダイに分かれた方が良いのかについての判断は非常に難しく、回路規模を考えるとツールに自動で判断してもらうほうが良い。Vivadoにはそうした機能なども搭載した」(同)とするほか、開発現場での設計変更に対し、各ツール間のデータを共通化することでデザインの一貫性を確保することを可能とし、開発容易性も確保している。

さらに、ASICを活用してきたユーザーでも使いやすいように、従来のVelilogやVHDLなどに加え、C/C++/System Cを用いた開発が可能となる。これにより、VelilogやVHDLに触れたことがなくC言語系しか使えないユーザーであっても、RTLの合成まで最適化したものを作製、検証することが可能となった。

加えて、全体的なパフォーマンスも向上しており、IPコアおよびシステムを中心としたインテグレーションと短時間での検証の実現、および決定的アルゴリズムを用いた高速かつ階層的なタイミングクロージャとECOフローによるインプリメンテーションの高速化により、従来の同社デザインスイート「ISE」の最新版となる「ISE 14」と比べて最大4倍の生産性向上が見込めるようになったほか、従来100万ゲート規模が現実的な解を出す限界レベルであったのが1億ゲートまで拡張することが可能になったという。

|

|

|

|

Vivadoを用いると従来のISEを用いた場合と比べて最大4倍の生産性向上が可能となる |

Vivadoではインテグレーションの高速化とインプリメンテーションの高速化の両側面から生産性の向上を実現している |

過去12カ月間にわたり、100社を越す企業がベータ版プログラムに参加し、国内からも複数社が参加しているという。実際に、初期バージョンとなる「Vivado 2012.1」を使用してみたOKI情報システムズ、東京エレクトロン デバイス(TED)、ペリフィケーションテクノロジーの3社がそれぞれ、自社のIPなどのインプリメントなどを行い性能確認を行ったところ、OKIの場合、ISE 14.1比でインプリメントのランタイム3.3倍、PC上のメモリ使用率1.2倍の向上効果が確認されたほか、デザインの集約率もISEではフロアプランがデバイス全体に拡散的に配置されていたが、Vivadoではデバイスの一部に集約されて配置されるようになったという。また、画像処理回路のベンチマークを実施したTEDでは、ISEでは1時間かかったところがVivadoでは30分で済んだほか、画像処理の速度を満たすための最適化に関するカットアンドトライがISEでは必要であったが、Vivadoでは一発で終えることができたという。そしてペリフィケーションテクノロジーでは、これまでに実際に開発した製品(8×8マトリクスを有したブロードキャスト用チップ)に対し適用したところ、ISEでは数十回のフィッティングが発生したがVivadoでは3~4回で済み、イタレーションが大幅に引き上げられたことが確認されたとした。

Vivadoが対応するのは同社の先端FPGA製品である「7シリーズ(Zynq含む)」以降の製品と同社では説明しており、これまでのVirtex-6以前のVirtexやSpartanなどはメジャーバージョンアップとしての開発は停止する(バグフィックスなどの対応は継続される予定)が従来のISE 14が引き続きサポートする形となる。

なお、Vivadoの製品パッケージとしては、IDEとSDKのほか、デバイス制限ありシミュレータを搭載した無償版「WebPACK」のほか、検証とデバッグ機能としてフル機能のシミュレータやロジックアナライザ/シリアルI/Oアナライザを搭載した「Design Edition」(2995ドル)、ハイレベル合成やDSPなどのIP生成にも対応した「System Edition」(4795ドル)の3種類が用意されており、2012年末までは、サポート期間内の既存のISEユーザーには追加料金なしその期間分、Vivadoを提供するという。