NECは、LSI実装のはんだ付け工程で、LSIパッケージや基板の反り、およびはんだの挙動を高速・高精度にシミュレーションする技術を開発したことを発表した。

同技術は、多層ばり理論を応用しプログラム化した解析ツールを用いることで、高温下のリフロー工程で生じるパッケージや基板の反りを高速に予測することが可能。また反りの予測結果と、分子動力学解析手法で解析したはんだ粒子の動きとを組み合わせることで、接続部の溶融はんだの挙動を高精度に可視化することができる。

LSIの薄型化や実装の高密度化、はんだの鉛フリー化によるリフロー温度の上昇により、パッケージの反りが増大し、接続不良(未接続、くびれ、ショートなど)の原因となっている。現在、はんだ接続部の構造設計や生産プロセス設計は、技術者の経験と勘により行われているが、パッケージの多様化や複雑化により、従来手法では最適な設計が困難になってきていた。

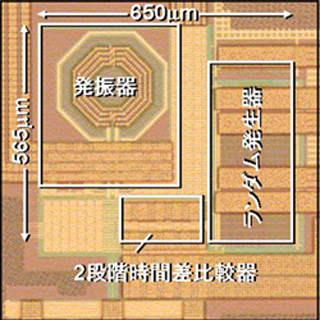

NECでは、LSIパッケージの構造に多層ばり理論を用い、素材の異なる多層パッケージの反りを高速に予測する解析ツールを開発。パッケージ全体を温度変化を受ける多層の「はり」とみなして解析するため、従来の有限要素法FEMを用いて細かく網の目状に解析する手法に比べて、1回の解析時間を1/60~1/90と短縮。これにより、最適な多層構造とリフロー条件を短時間で提示可能にした。また、同技術はプリント基板の反り予測にも適用可能となっている。

さらに、各粒子に働く力を合計して運動量を算出する分子動力学解析手法を応用し、パッケージと基板の接続に用いる溶融はんだを粒子で表現して、粒子間に働く力を求めることで挙動解析を実施。リフロー工程において、常に変化する温度・圧力・エネルギーなどを計算し、パッケージの反り予測結果も考慮しながら、高精度な溶融はんだ挙動の可視化を実現した。

これらの技術を組み合わせることで、はんだの接続状態をシミュレーションで再現、不良発生のメカニズムや要因分析を容易にすることが可能となり、高い品質を確保することが可能となる。また試作を繰り返す工程を削減し、設計リードタイムの短縮や開発コストの削減など、高効率な開発にも貢献できると同社では説明している。

なお、NECでは、ハードウェア製品の一層の高信頼性化に向け、同シミュレーション技術を用いた設計の開発を推し進めていくとしている。