ルネサス エレクトロニクスは、40nmプロセス世代以降のシステムLSI向けの新しいSRAM回路技術を開発したことを発表した。同技術の詳細は、2010年6月15~17日に米国ハワイ州で開催される半導体デバイスに関する国際会議「VLSI技術シンポジウム(2010 Symposium on VLSI Technology)」にて発表された。

同回路技術は、プロセス微細化に伴うデバイス特性バラつき増大の影響を低減するもので、微細化によるSRAMの小面積化のトレンドを維持することが可能となる。また同社では、同技術を活用し40nm世代の2MビットSRAMを試作、その動作を確認した。

デバイスの製造プロセスの微細化に伴い、デバイス素子の特性バラつきの影響が顕在化、特にSRAMは、この影響を受けやすく、従来技術の延長だけでは、SRAMを安定して動作させるための動作マージンが減少する。これまでは、動作マージンを維持するため、複数の電源制御回路をSRAMに付加することで、SRAMのワード線あるいはデータ線(ビット線)などを各々制御する方式などが提唱されてきたが、同方式では、デバイス素子が微細化されても、複数の電源制御回路の面積が大きいため、SRAM全体の面積低減が難しいという問題があった。

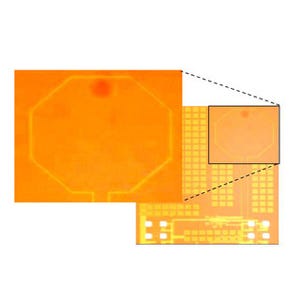

そのため同社では、「動作マージン劣化の影響を低減する多段階ワード線制御技術」および「高速化と小面積化を両立する階層SRAM回路技術」という2つの技術を開発、これを、40世代プロセスによる0.248μm2サイズの微小SRAMセルに適用、世界最高レベルの集積度となる2.98Mビット/mm2の2MビットSRAMを試作、安定動作を確認した。

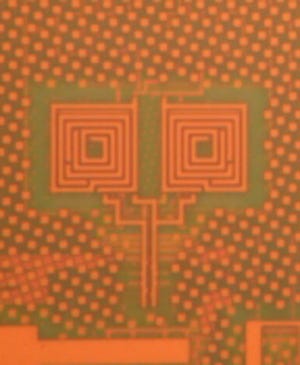

動作マージン劣化の影響を低減する多段階ワード線制御技術は、ワード線の電圧制御を時間的に複数段階に行い、従来方式で必要であった複数の電源制御回路を、ワード線のみを制御する回路に集約可能にした。この時、ワード線の電圧制御をゆっくり行うことで、デバイス素子の特性バラつきがあっても、SRAMの安定したデータの読出し・書込みが可能となった。また、電源制御回路をワード線のみで行うことで、SRAMの集積度を高めることが可能となった。

一方の速化と小面積化を両立する階層SRAM回路技術は、ビット線を複数に分割し、ビット線につながるSRAMセルの数を削減する階層SRAM回路技術を開発。分割されたビット線にはローカルセンスアンプという信号振幅増幅回路を付加し、本来存在するセンスアンプの動作を支援する構成とした。このことで、多段階ワード線制御で必要であったワード線のゆっくりとした制御で生じてしまうSRAMの動作速度の低下を防ぐことが可能となった。また、ローカルセンスアンプのレイアウトの工夫により、面積増加を最小限に抑えることができ、高い集積度を実現できたという。

同社では、低消費電力が求められる応用分野では、通常よりも低い電源電圧でSRAMを動作させることが要求されることから、これらの技術を用いることで低電源電圧化に伴うデバイス素子の特性バラつき増大の影響を低減できるため、特に低電源電圧のSRAMを実現する技術としても期待できるものとしており、今後、今回開発したSRAM回路技術をシステムLSIによる低コスト化と低消費電力化を実現するための基本技術とし、早期製品化を目指して研究開発を進めていくとしている。