Hot Chips 21の最後のセッションであるServer IIで、Sun Microsystemsは16コア、256同時スレッドをサポートする「Rainbow Falls」を発表した。初代「Niagara」、2世代目「Victoria Falls」に続く滝シリーズの3世代目のCMT(Chip Multi-Thread)プロセサである。

|

|

|

Rainbow Fallsについて発表するSunのSanjay Patel氏 |

この発表は、コア数、コアあたりのスレッド数を倍増することと、それに必要となるデータバンド幅の確保の挑戦にフォーカスした発表であると断り、チップの物理的な側面については、クロック周波数、消費電力はもとより、チップサイズ、キャッシュサイズなどにも言及されなかった。

16コア、256スレッド化の挑戦にフォーカスというのも分からなくは無いが、聴衆が皆、Victoria Fallsの発表の内容を覚えているわけでもないし、あまり具体的な数字を出さないで挑戦と言われてもピンと来ないということで、分かりづらい発表であった。多分、未発表の製品であるので、これらの具体的な情報は出すなという会社としての方針で、同氏としては苦しい発表であったのであろう。

Intelの「Nehalem EX」やIBMの「POWER7」では、コアとローカルな3次キャッシュが密に結合し、他のコアの3次キャッシュは距離が遠くなるという構造であるが、Rainbow Fallsでは、16個のコアと16バンクの2次キャッシュをクロスバにより等距離で接続する構成になっている。ただし、これらのコアと2次キャッシュを直接接続するためには16x16のクロスバが必要であり、面積が大きくなってしまい予定の面積で実現できない。このため、2つのコアと2バンクをそれぞれ1つのグループとして8x8(これに加えてキャッシュを介さないI/O接続のポートがあるのか、実際は8x9)のクロスバとすることにより面積をセーブして実現している。

そして、2次キャッシュ以降は2つの独立したコヒーレンスプレーンに分割されており、アドレスインタリーブされた形で並列に動作することができると思われる。また、各コヒーレンスプレーンは2個のコヒーレンスユニット(COU)を持っているが、どのような使い分けがされるのかについては明らかにされなかった。

そして、コヒーレンスユニットから他のノードに接続する高速リンク用の3つのバッファであるLFU 0~3 とDRAMコントローラに接続されている。

前世代のVictoria Fallsでは、他ノード接続は6.4GB/sのデータ伝送速度を持つ14レーンの高速シリアルリンクであったが、コア数が倍増しているので、これに対応して2倍程度の性能に増強されていると思われる。そして、メモリインタフェースはVictoria FallsではMCUあたりFB-DIMMが2チャネルであったが、これも2倍以上に増強されている可能性が高い。また、メモリとして、継続してFB-DIMMを使用しているのか、あるいはIntelやIBMのように外部にバッファチップを置いてDDR3を使用しているのかなどについても言及されなかった。

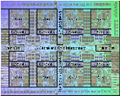

そして、チップの全体図として次の図が示された。外側の額縁の外部インタフェースとのバッファやSERDESの内側に上下2列に8コアずつが並んでいる。そしてその内側に2次キャッシュのデータアレイ、さらに2次キャッシュのタグアレイが配置され、中央にクロスバが配置されている。この配置の考え方はVictoria Fallsと同様である。

発表では明らかにされていないが、使用プロセスは45nmと言われている。そして、400平方mm程度のチップを想定すると、このチップレイアウト図に占める面積から見て2次キャッシュの総量は8MB程度ではないかと推測される。65nmプロセスを使うVictoria Fallsの2次キャッシュは4MBであったので、Rainbow Fallsで8MBは妥当なサイズである。

また、Victoria Falls(UltraSPARC T2、T2+)のクロックは1.2/1.4/1.6GHzであり、1世代進んだ45nmプロセスを使っているとは言え、消費電力を考えるとコア数を倍増したRainbow Fallsのクロック周波数は同程度ではないかと推測される。

今回の発表では性能についても言及は無いが、コアあたりの性能は前世代を下回ることは無く、チップ全体ではVictoria Fallsの2倍以上の性能を実現すると思われる。したがって、大規模なWebサーバのように超多数のスレッドが並列動作する用途や、大規模なスレッド並列化が可能な用途では威力を発揮すると考えられる。