Advanced Micro Devices(AMD)は、45nmのクワッドコアCPU向けトランジスタ技術を開発し、その概要をIEDM 2008で発表した(講演番号27.7)。同社が2008年11月13日に製品出荷を発表したクワッドコアの次世代Opteron「Shanghai」に採用されたとみられる。

新開発のトランジスタは、同社がこれまで採用してきたトランジスタ技術に比べ、動作速度が12%向上する(リング発振器ベース)。電流駆動能力を示す飽和ドレイン電流は、nMOSトランジスタが1.290mA/μm、pMOSトランジスタが0.820mA/μm(電源電圧1.0V、オフ電流100nA/μm)とかなり高い。

トランジスタ構造の特長は、拡散層(ソースおよびドレイン)のハロ(Halo)構造(短チャネル効果を抑制するための高不純物濃度領域。拡散層付近に設ける)をソース側だけに設けるとともに、ソースとゲートをオーバーラップさせたことにある。こうするとDIBL(Drain-Induced Barrier Lowering)が抑えられ、ドレイン電流が増加する。またホットキャリア効果が減り、トランジスタの寿命が伸びる。

AMDではこの非対称な(Asymmetrical)不純物プロファイルを備えたトランジスタ(FET)を「AFET」と呼んでいる。そのほかの基本技術は部分空乏(PD)型のSOI CMOSで、従来と変わらない。酸化膜換算のゲート絶縁膜厚は1.2nmである。また埋め込みSiGeによる歪みシリコン技術を採用している。

新開発のAFETをクワッドコアプロセッサの生産に適用したところ、歩留りは従来のトランジスタと変わらなかった。開発したトランジスタ技術は、32nmプロセスにも十分適用できるという。

|

|

|

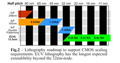

新開発のAFETをクワッドコアプロセッサの生産に適用する前と後での生産歩留りの変化。左下のチップ写真は論文集では明記されていなったが「Shanghai」とそっくりである(IEDM 2008の論文集から抜粋) |

なお日本AMDの吉沢俊介社長は11月13日の「Shanghai」発表時に「45nm SOIプロセスでは、すばらしいトランジスタができた」とコメントしており、このトランジスタはAFETのことを指すとみられる。