富士通研究所は12月16日、32nmプロセス以降のロジックLSI向けに、低消費電力化CMOS技術を開発したことを発表した。

従来、トランジスタの電源電圧を下げると、MOSトランジスタが流すことができるオン電流が減少し、動作速度の低下を引き起こす問題があった。

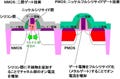

今回開発された技術は、既存の45nmプロセス世代の設備に、結晶面(110)面のSi基板を適用することで、既存の(001)面と比較して、NMOSのオン電流を減少させることなく、PMOSのオン電流を向上させることが可能になるというもの。

|

|

|

32nm世代以降向け低消費電力化CMOS技術 |

Siの表面処理として、ゲート絶縁膜形成前に施す熱処理時に通常とは異なるガスを用いて熱処理を行うことで、素子分離領域近傍に(111)面と(331)面を形成することに成功した。いずれの面のNMOSの移動度は(110)面の移動度よりも高いため、ゲート中央部が(110)面であっても、オン電流は10%の向上となる。また、PMOSのオン電流も移動度の向上により10%の向上が確認された。

|

|

|

トランジスタのゲート幅方向の断面と結晶面の関係 |

また、シリサイドの形成後にAlを注入することで、NMOSのシリサイドとSiのコンタクト抵抗が減少することを発見。Alをシリサイドの極浅領域に注入することで、NMOSのオン電流の20%向上を実現した。さらに、Siの表面処理技術と併用することで、(110)面のSi基板を用いても、(001)面と同等のNMOSのオン電流を実現した。

一方、PMOSのコンタクト抵抗はAlの注入により増加し、PMOSのオン電流が減少することも判明。そのため、NMOS領域に選択的にAlを注入するプロセスを構築し、PMOSのオン電流減少を防いだ。

|

|

|

今回開発された技術と従来技術の比較 |

これらの技術を用いた(110)面のSi基板採用LSIを試作した結果、従来の(001)面の場合に比べ、NMOSのオン電流を維持したまま、PMOSのオン電流を40%向上できることが確認された。これにより、電源電圧を10%下げても、動作速度は低下せずに消費電力が約20%削減できることが確認された。

また、同技術を45nmプロセスの製造工程に導入した場合、追加される工程はイオン注入と熱処理の2工程のみであり、32nmプロセス以降の製造工程に導入した場合でも、ウェハコストを除いた製造コストは1%以下の増大で抑えることができるという。

同社では、32nmプロセス以降の携帯機器向けシステムLSIやマルチコア・マイクロプロセッサなどへの適用に向け、実回路での評価を進めていくとしている。