TSMC - 順調に製品が投入された16nmの「次」

AMDがほぼ全面的にGLOBALFOUNDRIESに移った結果として、PC系ではNVIDIAのGPUが利用するだけとなるのがTSMC。実際にはSSDのコントローラとかEthernet、チップセットなどに広くTMSCのFabは利用されているが、先端プロセスに関してはモバイル向けやサーバー向けのSoC、それとGPUということになる。

さて、そのTSMCであるが、16nmに関しては、すでにPascalベースの製品が大量出荷されており、またモバイルSoCやサーバー向けSoCも量産が行われており、焦点は次の16nmと、その次に来る10nmになる。

まず16nm。当初リリースされたのが16FFであるが、これはあまり多く使われず、続く16FF+が広く利用されることになった。ただ16FFにしても16FF+にしても、製造の初期コスト(主にマスクコスト)が非常に高いうえ、製造コストそのものものも下がりにくい(FinFETの構築には何度もパターニング→エッチング/CMP→積層を繰り返す必要がある)という問題があった。

そこで、初期コストや製造コストを下げられる(ただし性能も若干下がる)ものを16FFCとして準備してきており、こちらも量産が始まっている(Photo05)。

|

|

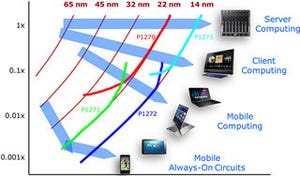

Photo05:TSMCのロードマップ。これはARM TechCon 2016における同社のプレゼンテーション資料より。各々の箱の左端がRisk Productionの始まった時期で、右端には意味がないそうである |

もっとも16FF+と16FFCでは製造方法が一部異なるので、16FF+のマスクをそのまま流用して16FFCとは行かない。そもそも電気的特性も異なるので、最適化技法が異なることになる。「いま存在する16FF+ベースの製品をそのまま16FFCに移行させて低価格化」というわけにはいかない。

したがって、量産工程で製造中のものは、いずれも16FFC向けに設計されたメインストリームやバリュー向けの製品である。このあたりは16FF+向けIP(Photo06)と16FFC向けIP(Photo07)を比較してみると分かりやすい。

これが直接PC向け製品に影響があるか? というと、SSDのコントローラなどには一部使われる可能性に加えて、もしNVIDIAがVoltaの世代でも16nmを使う場合、ハイエンドは16FF+のままだろうが、ローエンドは16FFCという可能性も否定できない。あるいはハイエンドが10FFに移行したとしても、バリューは引き続き16nmに留まると思われるので、この場合も16FFCは良い選択肢となりえる。

TSMC - 10nmの量産はすでに開始

さて本題は10FFである。先のPhoto05にもちょっと出てきているが、TMSCは2016年のQ2にRisk Productionを開始している。Samsungは10月に10LPEの量産を開始したことを発表しているが、TSMCもAppleやMediaTek、HiSiliconといったメーカー向けに量産を始めており、2017年の早い時期の大規模量産が開始されると見られている。

その10nmであるが、TSMCによれば16FF+と比較してエリアサイズを52%に、性能を15%アップ、ないし40%の電力削減が可能(Photo08)としており、これが本当に実現できれば非常に有望である。

|

|

Photo08:CPP(Contacted Poly Pitch)×Mx(Metal Pitch)が縦軸、Risk Productionの時期が横軸である。Foundry AがIntel、Foundry BがSamsungであろう |

ちなみにこの表における掛け算であるが、これはASML standard node Formula、あるいはただ単にASML Formulaとして知られている計算である

Standard Node=0.14×(CPHP×MMHP)^0.67

を意識したものであろう(CPHP:Contacted Poly Half-Pitch, MMHP:Minimum Metal Half-Pitch)。これを厳密に計算すると、各社の10nmは

- Intel : 9.5nm

- TSMC :11.3nm

- Samsung:12.0nm

相当になるというもので、まぁ一番攻めているのはIntelであるが、その分投入時期も遅い。TSMCとSamsungは同時期に投入されるが、TSMCの方が微細化がされている。

不安要素は、TSMCの10nmを疑問視するメーカーが少なからずあることだ。XilinxとAPM(Applied Micro)は、次期製品について10nmをスキップし、7nmで製造することを明確に表明している。

また、GLOBALFOUNDRIESのように10nmの提供をやめて、7nmで追いつくことを目論んでいるメーカーもある。実のところ10nmに積極的なのはSamsungとIntelだけという話はこちらの冒頭にも書いたとおりだ。

なぜ10nmをスキップして7nmに向かうという判断をしたのか、その理由は明かしてくれなかったが、20nm世代のように性能向上あるいは消費電力低減が可能な動作条件が非常にタイトで、これを外すと性能低下とか消費電力増加が起こりやすい、もしくは16FF+→10FFの改善率が予想よりも低いので効果が薄いと判断した、といったあたりがぱっと思いつく。

余談になるが、TSMCの20nmの場合、QualcommのSnapdragon 810では発熱の多さが問題になったが、同じくTSMCの20nmを使うOracleのSPARC M7は32コア構成で4.1GHzでブン廻しつつ、消費電力を常識的な範囲に抑えている。これは、設計の側でどこまで20nmをうまく使うかによって性能/消費電力比が揺らぎやすいプロセスであることを物語っている。

時間を掛けて最適化すれば、20nm同様に10FFもそれなりに性能が出るのかもしれないが、そこまで時間を掛けられない顧客が少なからずいるということだろうか?

TSMC - 7nmを前倒しで進める

実際TSMC自身もこれに対応してか、7nmのRisk Productionを2017年の第2四半期に開始する予定をPhoto05で示しており、基本的なIP(Photo09)や開発環境(Photo10)の整備に余念がない。

これが予定通り進むと、TSMCの10FFは、20nmがそうだったように、次の7nmへの繋ぎという感じになって、10FF+とかは出ないで終わるかもしれない。「NVIDIAがVoltaを16FF+で」という話が出てくるのは、このあたりも絡んでいる可能性がある。