Intel Knights Landingメニーコアプロセサ

Oakforest-PACSは、「Knights Landing(KNL)」という名前で開発されてきたIntelの「Xeon Phi 7250」メニーコアプロセサを計算エンジンとして使っている。Xeon Phiは、後述のように、これまでにないアーキテクチャの計算エンジンであり、これが実アプリケーションでどのような性能を発揮するかは興味深い。

KNLを使うスパコンとしては、前回6月のTOP500で116位となったテキサス大TACCの「Stampede-KNL」があるが、11月のTOP500では、5位のローレンスバークレイ国立研究所のCori、そして6位のOakforest-PACSと2台の大型Xeon Phiスパコンが登場した。

IntelのKNLであるが、次の図のように、36個のタイルと、4個のMCDRAMのコントローラ、合計6チャネルのDDR4メモリコントローラ、合計36レーンのPCI Express 3.0インタフェースなどを集積している。各タイルは、図の右上に示すように、2個の、コアと2個のVPUのグループが、1MBのL2キャッシュとCHA(Caching/Home Agent)を共用するという構造になっている。

CPUコアは、Xeonと命令互換で、アプリケーションだけでなく、OSも走らせることができる。前世代の「KNC(Knights Corner)」はOSを走らせることはできず、Xeon CPUに接続して使うアクセラレータという位置づけであったが、KNLはCPUとしても使えるプロセサとなっている。

VPUは512bit長のSIMD演算FMA演算を実行することができ、64bit長の倍精度浮動小数点演算なら8命令、16演算を並列に実行することができる。したがって、2基のVPU合計では32演算が実行でき、32演算×68コア×1.4GHz=3.0464GFlopsのピーク演算性能を持つ。

この図を注意深く見ると、実はタイルは38個ある。しかし、その内の2個は不良タイルのスペアなどのために使われ、製品としては最大36タイル、72コアということになっている。なお、CoriやOakforest-PACSが使用しているXeon Phi 7250は68コアの製品であり、34タイルを使うチップである。

そして、この最大36タイルとメモリコントローラ、PCI Expressなどを2次元のメッシュネットワークで接続している。前世代のKNCは、コア間の接続にリングバスを使っていたが、KNLでは2次元メッシュでの接続に変わった。KNCに比べて、バンド幅が改善されていると考えられるが、Intelからは具体的な数値は公表されていない。

そして、もう1つの大きな改善は、MCDRAMというメモリを使っている点である。MCDRAMは、DRAMチップを4枚積層してTSVで接続したメモリで、次の図ではStreamベンチマークで400GB/s以上という高いメモリバンド幅を持つと書かれている。メモリバンド幅という点では、NVIDIAのP100 GPUが使用しているHBM2と近いが、HBM2がメモリだけの集積であるのに対して、MCDRAMは、後述のように、キャッシュとして使えるようにタグRAMを内蔵している点が特殊である。

Xeon Phi 7250は、合計16GBのMCDRAMに加えて、最大6枚のDDR4 DIMM(Oakforest-PACSの場合、16GB DIMMを使い合計96GB)を接続することができ、CPUのメインメモリとして大量のデータを扱うことができるようになっている。

|

|

|

Knights Landingの概要。最大72コアを集積し、各コアは512bit SIMD演算を実行する2基のVPUを持つ。メモリとして3D積層の400+GB/sという高バンド幅MCDRAMを装備する (出典:Hot Chips 27におけるIntelのAvinash Sodani氏の発表スライド) |

次の図は、KNLのコアとVPUのブロックダイヤグラムで、CPUコアは2命令を並列処理するOut-of-Orderコアである。そして、Xeonの(トランザクション処理以外の)すべての命令を実行できる。また、KNLのコアは、4スレッドを並列に実行するSMT(Simultaneous Multi Thread)コアとなっている。

2基のVPUはコアの命令フェッチ、デコード、Out-of-Orderの命令発行機構などを共用し、コアの演算器と同じ位置づけで使用することができる。

GPUの場合は、GPUの演算器とメモリは、CPUとは分離されており、明示的にCPUとGPUのメモリの間でデータのコピーを行う必要があるが、KNLではCPU機能を実行するコアと、高性能の演算を行うVPUが同じメモリを使うので、別個にメモリ領域を確保し、データをコピーする必要が無くなり、GPUと比べるとプログラミングが大幅に楽になる。また、PCI Express経由のCPUメモリとGPUメモリの間のデータ転送が不要になるので、性能的、消費エネルギー的にも有利である。

|

|

|

コアとVPUのブロック図。2命令を並列処理するOut-of-OrderのXeon命令互換のコア。2基のVPUは、コアの演算器と同じ位置づけで、GPUのように、CPUとアクセレータ間のメモリ転送が不要である (出典:Hot Chips 27におけるIntelのAvinash Sodani氏の発表スライド) |

KNLのメモリのMCDRAMの使い方には、次のような3つの使い方がある。第1のキャッシュモードでは、MCDRAMがDDR4メモリのキャッシュとして動作する。第2のフラットモードでは、MCDRAMとDDR4メモリは異なるアドレスを占め、KNLのアクセスするアドレスで、どちらのメモリを使うかが決まる。

そして第3の使い方は、ハイブリッドモードで、MCDRAMの1/4、または、半分をキャッシュとして使い、残りはフラットモードとして使うという方法である。

MCDRAMはDRAMで作られたメモリであり、そのアクセス時間はDDR4メモリと大差ないので、キャッシュとして使ってもアクセス時間が短縮できるわけではない。しかし、DDR4メモリのメモリバンド幅は90GB/s程度であり、これを超えるアクセスが集中するとアクセス時間が急激に増加する。これはいわゆる渋滞の状態である。これに対して、MCDRAMをアクセスする場合は、480GB/sまでアクセス時間は漸増である。

高頻度でアクセスされる領域がはっきり分かっている場合は、フラットモードを使い、高頻度アクセスする領域をMCDRAMに割り付けるのが良く、高頻度アクセスされる領域がばらばらの場合はキャッシュモードを使うのが良さそうである。

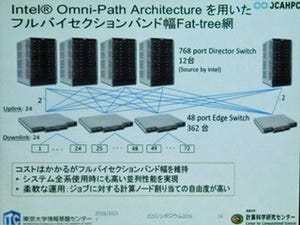

そして、IntelはKNLと合わせて、Omni-Pathというインタコネクトを提供した。データ伝送速度は100Gbit/sで、この点ではEDR InfiniBandと同じであるが、MellanoxのEDRエッジスイッチは36ポートであるのに対して、IntelのOmni-Pathエッジスイッチは48ポートとポート数が多く、同じ規模のシステムを構成するために必要となるスイッチの数が少なくて済み、Intelは、スイッチの通過レーテンシが33%小さくなると謳っている。

次回は2016年12月22日に掲載予定です。