LOCとTOC

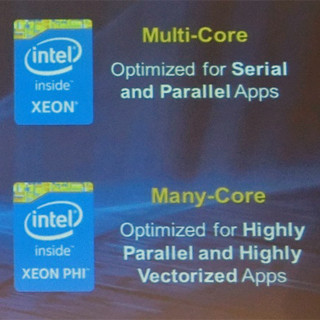

CPUはシングルスレッドの実行を速くすることに最適化した「Latency Optimized Core(LOC)」である。一方、GPUは多数のスレッドを並列に実行するプロセサであり、個々のスレッドの開始から終了までの時間ではなく、単位時間にどれだけ多くの命令を実行できるかを重視した「Throughput Optimized Core(TOC)」である。

NVIDIAのGPUを使うシステムは、このLOCとTOCを組み合わせた形となる。このような形とすると、LOCのCPUとしては、軽量のものから大型のものまで自由に選ぶことができる。また、LOCのメモリとしてはレーテンシに最適化したものを使うことができる。

一方、TOC側は設計の選択の幅が広く、性能、電力、チップサイズなどを最適化した設計とすることができる。また、メモリはCPUのメモリとは別に設けるので、両方のメモリアクセスが同じメモリを使い、干渉するという問題がない。

図4.6はこのLOC+TOCのシステム、Intelの「Xeon Phi(MIC)」のような性能の低いプロセサ(ここではLOCの25%の性能を想定)だけを使うシステムとLOCだけのシステムの性能をAmdahlの法則を使って比較したものである。上側の図はプログラムの98%が並列に実行できる場合で、直列に実行しなければならない部分は2%だけという場合である。一方、下の図は並列に実行できるのは90%で、10%は直列に実行しなければならないという場合である。

上の図では、LOCで実行する部分は2%だけであり、緑の部分は小さい。小規模コアを使うMICの場合は、性能がLOCの0.25倍であるので、緑の部分の時間が4倍になっている。

並列化可能な青の部分は、LOCだけのシステムではLOCで直列に実行せざるを得ないので長い時間が掛かっているが、LOC+TOCのシステムではTOCで並列に処理できるので、この時間は短くなっている。

MICの場合も多数のコアで並列に処理できるのであるが、青の部分の長さがLOC+TOCのグラフより小さくなっているのは何故だか分からない。GPUよりもMICの方が並列処理の効率が高いように見える図はNVIDIAの図としては変である。

下の図は90%が並列実行が可能な場合で、LOCだけのシステムでは10%が緑の直列実行、残りの90%が並列実行の時間というグラフになっている。そして、LOC+TOCの場合は青の部分がTOCで並列実行されるので0.9くらいになっている。MICのシステムでは緑の部分が4倍になり、ここでも青の部分はTOCより短い時間となっている。

しかし、どちらの図でもLOC+TOCはMICよりも速いという図になっており、仮に並列処理の場合、MICがTOCより速いとしても、色々な並列度のプログラムがあることを考えると。LOC+TOCの方が良いという図にはなっている。

図4.7は米国を代表するNERSCのEdison、Oak RidgeのTitan、ArgonneのMiraとこれらの次期システムであるNERSCのColi、Oak RidgeのSummit、ArgonneのAuroraの諸元をまとめたものである。SummitとAuroraはピーク性能や消費電力の点ではほぼ同じ規模のスパコンであるが、SummitはIBMのPower9とNVIDIAのVolta GPUを使うLOC+TOCシステム、AuroraはIntelのKnights Hillを使うMICシステムである。

軽量ノードか大型ノードか?

Summitのノード数は約3,500であるのに対して、Auroraは約50,000ノードと14倍ノード数が違う。つまり、Summitは大型のノードであるのに対して、Auroraは軽量ノードのシステムとなっている。

Oberlin氏は両者の得失については分析せず、5億ドル(SummitとAuroraの予算)を投じるノードアーキテクチャの実験であるとだけ述べていた。

図4.8の左側の表はSummitとAuroraの諸元を抜き出したものであるが、内容が微妙に変わっている。Auroraのシステムメモリに関しては、図4.7では>7PB DRAMと書かれているが、図4.8ではDRAMとHBMを合わせて2.8PBとなっているのであるが、この理由は分からない。

そして、Summitのメモリは1.74PBとして、ノードあたりのメモリを4.97E+11(バイト)、Auroraのメモリは2.8PBとしてノードあたりのメモリを5.6E+10(バイト)と計算している。通信量が体積(ここではノードあたりのメモリ量)の1/3乗(立方根)比例すると想定すると、SummitのノードはAuroraのノードの約2.1倍のバンド幅が必要という計算になる。

しかし、表面と体積の関係であれば、表面は2乗、体積は3乗であり、表面は体積の2/3乗に比例するはずであり、1/3乗ではないと筆者は思うのであるが、ここでは、発表のまま紹介する。

NICは必要か

最後のトピックはNIC(Network Interface Card)が必要かという考察で、NICはLOCのエージェントで、リモートDMAなどをサポートし、データ転送と計算処理を並列に実行してネットワークのレーテンシを隠ぺいする効果がある。しかし、TOCは、多数のスレッドを並列に実行し、入力データが到着していなければ他のスレッドを実行することでレーテンシを隠ぺいすることができる。このため、TOCにとっては通常のNICはムダである。TOCの場合は、NICを使ってGet/Putで通信を扱うよりも、グローバルアドレスを使ってLoad/Storeで他のノードのメモリをアクセスし、Atomicもこのレベルでサポートする方が良いと考えられる。

しかし、NICを使わない場合、現在のスパコンでは標準になっているMPIをどうするのかという問題はある。

Oberlin氏の発表はおおむねSummitの構成の優位性を主張するもので、Exascaleのノードをどうすべきかという考察はあまり聞かれなかった。