ISC 2015においてIntelのAlan Gala氏が、「将来のシステムの方向性(Future System Directions)」と題して講演を行った。Alan Gala氏はIBMでBlue Geneのアーキテクトとして活躍し、2010年にはSeymour Cray賞を受賞した高名なアーキテクトであるが、IBMがBlue Geneから撤退し、現在の所属はIntelとなっている。

|

|

|

|

図3.1 ISC 2015において講演を行うAlan Gala氏 |

図3.2 メモリアクセスの重要性、データ移動の低電力化、消費エネルギーを低減するプログラミングモデルなどを中心に将来のシステムの方向性を述べた (以下の図の出典:ISC 2015におけるGala氏の講演スライド) |

メモリの高バンド幅化はアーキテクチャを変える

図3.3はTOP500の1位のスパコンのメモリバンド幅(B)と演算性能(F)の比をプロットしたものである。全体的にB/F比は減少する傾向にあり、最近の2回のTOP500のシステムでは通常のDIMMではなく、GDDRメモリを用いてB/F比を引き上げている。

高バンド幅のHBMは図3.4に示すように、DIMMと比較すると、バンド幅は約16倍である。ビット当たりのコストは、まだ、1.2~1.5倍であるが、バンド幅あたりのコストは1/10~1/40である。このため、新しい高バンド幅のメモリは、ハードウェアのアーキテクチャを変えつつある。

Knights Landingを見ると、中央にCPUがあり、それを同一パッケージに搭載された高バンド幅のDRAMが取り巻き、その外側にDIMMがあるという構造になっている。しかし、CPUには多数のコアが含まれ、MPIを使う場合も、1個のCPUに複数のMPIノードが含まれることが多い。つまり、全部のコアが1つにまとまっている必要性は、ほとんど、存在しない。

そして、図3.6のように、4分割したCPUそれぞれに高バンド幅DRAMを4個ずつ付けるというように再構成する。この図では、メモリバンド幅が15倍になると書かれているが、図3.4との比較では4倍であるし、DIMMだけを使う場合との比較なら40倍程度となり、この記述が何と比較しているのかは不明である。また、コアあたりのメモリ容量は減っていないと書かれているが、4チップをスタックする高バンド幅メモリを4個というのはDIMM 1枚程度の容量であるので、コアあたりのメモリ容量も減少すると思われる。しかし、非常に高いメモリバンド幅を持ち、元のCPUにDIMM 4枚分程度の容量の、相当なサイズのメモリが付いているシステムとなることは間違いない。

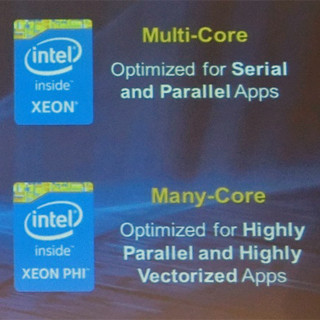

Gala氏は、ここでCPUのコア数を増やしたくなるかも知れないが、コア数を増やすと消費電力が増えてしまう。コア数を増やしても他の資源を増やすことは出来ないので、汎用の処理の性能をあげることはできないことを認識すべきであると言う。

|

|

|

図3.6 4分割したCPUにそれぞれ4個の高バンド幅DRAMを付ける。メモリバンド幅は15倍になり、コアあたりのメモリ容量も保てる。コアを増やしても汎用の性能が上がるわけではないことを認識することが重要 |

また、新しいメモリはエラー訂正などの新機能を組み込み信頼性、可用性を高めることが期待される。さらに、メモリ並のバンド幅とストレージ並の容量を持つメモリができると、IOの性能を大幅に高めることができ、チェックポイントの作成なども高速になる。このような新しいメモリは、ビッグデータ処理とHPCのプラットフォームを共通化する。

そして、これまでのDRAMはビット単価の低減だけを目標にしてきたが、これに容量当たりのバンド幅が目標に加わる開発に移行することによって、より良いメモリが作られることが期待されるという。