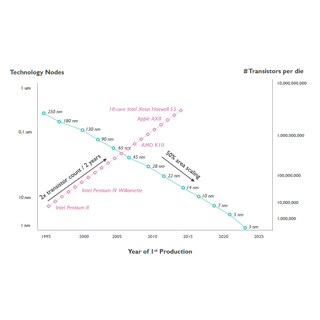

IC Knowledgeの視点でとらえた10nm以降の技術ノードでの問題点や注目すべき点を箇条書きで以下にまとめて示す。

商用ロジックノード10nm (標準ノード12nm相当)

- TSMCは、このプロセスノードを7nmへ移行するまで短期間使う予定の暫定的なノードとしているが、Samsungは長く使い続ける考えで、いくつものバリエーション(高速向けや低消費電力向けなどに応じた別々のプロセス)を整備する。GFは、10nmノードをスキップして14nmから7nmへ直行する。Intelの10nmは他社より配線微細化を進化させてトランジスタ特性を売りにする(注2)。

(注2) Intelは8月16日(米国時間)、英ARMとの提携により、Intel Custom Foundryの10nmプロセスでARMベースのモバイル向けSoCを製造すると発表した。その一環として、ARMの「Aristan Physical IP」の設計も利用可能にする。Intelは名を捨てて実を取った格好だ。これによりAppleやQualcommなどに向けたプロセッサも製造できるようになるため、今後、ファウンドリとしての競争はさらに熾烈になるだろう。

- このノードへの微細化により、集積密度と性能の両面で16/14nmより利点があることが実証されている。

- コンタクト抵抗の最適化とサイドウォールスペーサーのk値の低減が必要である。

商用ロジックノード7nm (標準ノード9.2nm)

- 微細化により性能を確保するのが難しくなっている。

- ビアとコンタクト形成にコバルトを採用するようである。

- 性能確保のためにP型MOSトランジスタのチャネルにSiGeを採用する可能性がある。

- Samsungは7nmからEUVリソグラフィを使うと言っている。

- Intelの7nmは標準ノードが5.9と小さい値なので(最小線幅が他社より狭いので)生産は2020年にずれ込むだろう。

商用ロジックノード5nm (標準プロセス7.1nm)

- FinFETを用いる限り、性能を確保するのが非常に困難である。

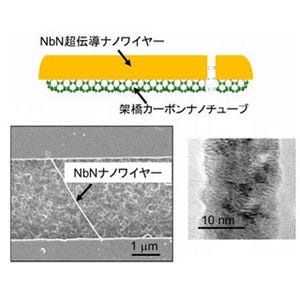

- PMOSチャネルにSiGeを用いるか、トランジスタ構造を横型ナノワイヤへ移行する見込みである。

- EUVリソグラフィが採用される見込みだが、同時に横側ナノワイヤを採用したくはない。

- 横型ナノワイヤを導入する前に、EUVだけで1/2ノード分だけ縮小する可能性がある。

NANDは3D積層の競争が激化

従来型(2D)NAND型フラッシュメモリの16nm/15nmを超えた微細化は経済的ではない。そこで、各社とも3次元積層化により、ビット密度(Gb/mm2)を継続的に増加させようとしている。今後も図1に示すようにビット密度は増加を続けて、最終的には3Dによるテラビット・チップの実現可能性がある。一方、2007年に世界で初めて3D NAND構造を学会発表した東芝が、2次元での微細化に固執したため3Dでは最後発になっている。

|

|

|

図1 Micron、Samsung、東芝のNAND型フラッシュメモリの記憶容量(Gb/mm2)の変遷。2015年までは予測、2016年以後は計画値。東芝の3Dは、この図が作成された時点では未発表であったため含まれていない (出所:IC Knowledge) |

3D NANDのロードマップの例(Intel/Micron連合の場合)を表3に示す。

Intel/MicronはCMOS周辺回路をメモリアレイの下に配置して、ダイ上のメモリアレイの面積の割合を増加できるが、メモリアレイ領域のストレスを増加させるので、いまのところIntel/Micronしか採用していない。積層レイヤが増えるにしたがって、チャネル移動度が小さくなるので、いずれはInGaAsのような高移動度材料に置き換える必要がでてくるだろう。

|

|

|

表3 Intel/Micron連合の3D NANDフラッシュのロードマップ。最左欄上から、西暦(年)、スタック数(積層したチップ数)、スタック当たりの層数、総層数、セルあたりのビット数、チャネルの構成材料(poly-Siあるいは高移動度材料)、周辺ロジック回路の位置(メモリアレイの下)、密度(Gb/mm2 (出所:IC Knowledge) |

2Dおよび3D NANDフラッシュメモリを製造するのに必要な設備投資額のプロセスカテゴリ別割合(%)を図2に示す。3Dの場合は、リソグラフィの負担は減るが、深堀りエッチングして多層メモリ膜を堆積した柱状電極を埋め込むために、ALD(Atomic Layer Deposition:原子層堆積) /CVD(Chemical Vapor Deposition:化学的気相堆積)/ドライエッチの比率が倍増する点が注目される。これらの分野の製造装置メーカーに商機が訪れている。