Hot Chips 27において、ウィスコンシン大学マディソン校のKaru Sankaralingam准教授がオープンソースの「MIAOW GPU」について発表を行った。MIAOWという名前は、論文のブラインド査読(著者が分からないようにして査読する)の際に使われた「Many-core Integrated Accelerator Of the Waterdeep」の頭文字を取ったものだと言う。しかし、MIAOW(日本語ではミャーオ)プロジェクトのマークはこの図のように猫の図案であるし、FPGAでの実装版は「NEKO」という名前を付けており、この名前は気に入っているようである。

ソフトはGNUやLinuxなど古くからオープンソースのものがあり、GoogleやFacebookなどでもオープンソースの利用がビジネスを支えている。ハード側でも「OpenCores」や「RISC-V」などのオープンソースCPUがある。しかし、GPUにはオープンソースのものが無いということからSankaralingam准教授のグループはMIAOWの開発を進めたという。当初は7人のグループで、12カ月で基礎を作り、その後、FPGAのエキスパートなどを加え、36カ月で現在の状態になったという。

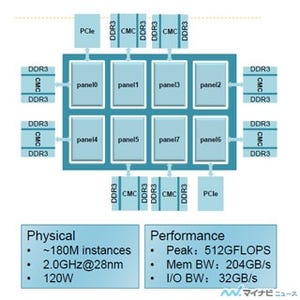

MIAOWの開発に当たっては、命令セットが公開されているAMDのSouthern Island GPUと命令互換のGPUを開発することにしたが、現状のMIAOWは3Dグラフィックス用のパイプラインや機能ユニットは、まだ、実装されていない。また、MIAOWの設計では、チップ面積、電力、クロック周波数、性能などを最適化することは目標としていないとのことである

MIAOWの命令セット

MIAOWの命令セットは、次の図に示した、AMDのGCNアーキテクチャの命令セットのうちの95命令を実装している。いわゆる科学技術計算などを実行するGPGPUとして必要な命令は実装しているが、3Dグラフィック向けの命令は、現状では実装していない。また、科学技術計算向けでもサポートしているのは32ビットの単精度浮動小数点演算だけであり、64ビットの倍精度の浮動小数点数はサポートしていない。

MIAOWハードウェアの構成

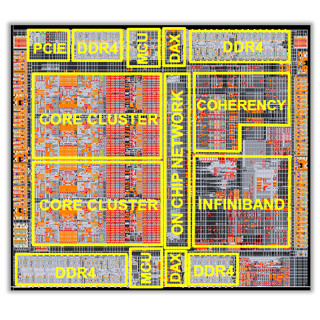

MIAOWは、次の図のように、「Ultra-threaded Dispatcher」という多数のスレッドを管理するユニットに「CU(Compute Unit)」と呼ぶ演算ユニットが付くという構成になっている。MIAOWは32個のCUを持つが、紙面の都合で、図には8個のCUしか書かれていない。そして、DispatcherやCUにデータを供給し、CUのストアデータを格納するL2キャッシュがある。L2キャッシュには3つのメモリコントローラが付き、そこからGDDR5のデバイスメモリに繋がっている。

右側はCUの内部を示す図で、命令をフェッチ、デコードして実行をスケジュールするユニットがあり、2段目には命令を実行するLSU((Load Store Unit)、演算を行うベクタALUと浮動小数点の積和演算を行うユニットとスカラのALUがあり、3段目にはローカルメモリ(Local Data Store)、ベクタ用GPR、スカラ用GPRが描かれている。

AMDのGPUでは並列に実行される64本のスレッドを「Wavefront」と呼んでいる。これは、サイズは2倍であるが、NVIDIAが「Warp」と呼んでいるのと同じものである。

次の図はMIAOWのCUのハードウェアの構造を示す図で、CUは40 Wavefrontをハードウェアで管理し、各Wavefrontの次に実行する命令のアドレスを指すPCを持っている。そして、このPCを使って命令を読み出し、Wavepoolに格納する。そして、Decode and Dispatchユニットは、全スレッドで命令を実行する条件がそろったWavefrontを選択して、実行ユニットに命令を発行する。

各実行ユニットは、自分宛の命令を実行して、結果をレジスタファイルやLDSなどに書き出す。

|

|

|

CUの構成。64スレッドのWavefront 40個をハードウェアで管理する。16WideのベクトルALUを8基(0-7)持つと書かれているが、これは4基(0-3)の間違いと思われる。そして、512エントリのSGPR、1024エントリのVGPRを64枚とLDSを持つ |

各CUハードウェアは、管理する40本のWavefrontの中から次の命令が実行可能であるものを、原則的にはラウンドロビンで選択して、オペランドで指定されたレジスタのデータと、PCが指す命令の命令コード、結果を格納するレジスタなどの情報を実行ユニットに渡して実行させる。

MIAOWはAMDのGCNアーキテクチャのGPUと命令互換であり、OpenCLのプログラムは変更なしに動作する。また、AMDのAPP SDKのOpenCLベンチマークも全てそのまま動作する。

また、MIAOWは、命令の追加などの拡張が容易な造りになっている。

(次回は9月22日に掲載します)