ケイデンス・デザイン・システムズは9月11日、モバイルおよび高性能コンピューティング(HPC)プラットフォーム向け7nm FinFET Plus設計の技術革新を強化するために、台湾・TSMCと協業していることを発表した。

ケイデンスのデジタル、サインオフ、およびカスタム/アナログツールは、TSMC 7nm FinFET Plusプロセス最新バージョンに対する認証を取得し、また、同社のライブラリーキャラクタライゼーションフローの強化も実現している。

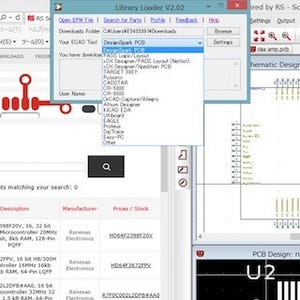

また、デジタルインプリメンテーション、およびサインオフツールは、TSMCにより7nm FinFET Plusおよび7nmプロセス向けに認証されており、PDK(process design kit) はダウンロード可能となっている。

7nm FinFET Plusプロセス向けに特化して開発されたツールの機能には、EUVレイヤー対応、ビアピラー対応の拡張が含まれ、7nmプロセス向けのデジタルおよびサインオフフローの強化には、配線密度およびIRを考慮した配置、クロックバッファー・クラスタ/配置/配線の強化、実行時間およびDRC (デザインルールチェック)品質を改善するNanoRouteツールのエンジン強化が含まれる。

認証されたカスタム/アナログツールが提供するデバイスのスナッピング、および高速カスタム配置配線フローにより、ユーザーは生産性を向上し、消費電力、マルチパターニング、集積度、EM(エレクトロマイグレーション)の要件を満たすことが可能となる。

Virtuoso Advanced-Node Platformの設計手法を強化し、新機能を利用することで、ユーザーは7nm FinFET Plusおよび7nmプロセステクノロジーを使用して設計を行う際に、従来のnon-structured設計手法と比較してカスタムフィジカル設計のスループットを向上することが可能となる。先行ユーザーは、マルチパターニングおよびカラーを考慮したレイアウト、モジュールジェネレーター(ModGen) デバイスアレイ、FinFET自動配置、ばらつき解析など、ツールの先端ノード機能を使用することにより、16nmプロセスと同程度のサイクルタイムを維持できる。

TSMCの7nm FinFET Plusおよび7nmプロセステクノロジーで認証されたツール群に加えて、Virtuoso Liberate Characterization SolutionおよびVirtuoso Variety Statistical Characterization Solutionの確認も行われており、7nm FinFET Plusプロセス向けの高度なタイミング、ノイズ、パワーモデルを含む高精度Libertyライブラリーを提供する。

同ソリューションは、Liberty Variation Format(LVF)モデルのキャラクタライズに対応する革新的な手法を利用しており、低電力アプリケーションの高精度なプロセスばらつきサインオフや信号線のエレクトロマイグレーション最適化およびサインオフが可能となるEMモデルの生成も可能にしている。