レノボ大和研究所およびレノボグローバル本社は2月7日、PC製造時のエネルギー削減と電子部品の信頼性を高めることを目的に開発した低温はんだ付け(LTS:Low Temperature Solder)プロセスを発表した。

RoHS規制などの環境規制によりはんだは鉛の含有ができなくなり、すずなどを含むものを用いる必要があるが、高温ではんだ付けを行う必要があり、電子部品へのストレスとなるなどの課題があった、

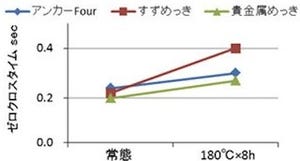

今回のLTSプロセスは、はんだペースト素材(すず、銅、蒼鉛、ニッケル、銀、および特有の組成からなるフラックスの混合物)について数千通りの組み合せを試す一方で、独自の熱プロファイル(経過時間と温度変化の組み合せ)に関する研究から実現されたもの。これによりプリント基板と電子部品をはんだ付けする熱の最高温度は従来比で70℃低い180℃へと下げることが可能となったほか、既存のリフロー炉などが流用できることも確認したという。

また、同プロセスを用いると、CO2排出量が低減できることも確認。すでにThinkPad E シリーズならびに第5世代X1 Carbonの製造で採用されているとするほか、2017年中に8基のSMT(Surface Mount Technology:表面実装技術)ラインに導入する予定としており、これによりCO2排出量は最大35%削減できる見通しだとしている。さらに、2018年末までに同プロセスを採用し、ラインごとに2台のリフロー炉を備えるSMTラインを33基適用することを計画しており、これが実現されると、CO2の年間排出量を5956トン削減することができるようになるとしている。

加えて、同プロセスを活用することで、過熱工程によるストレスが低減されることとなるため、プリント基板のそりが50%減少し、不良率(ppm)も減少することをプロセス導入初期から確認されているとも説明しており、これにより、PC製品の信頼性向上につながることも期待されるとしている。

なお、同社では、同プロセスはプリント基板を使用するエレクトロニクス製品すべてに例外なく適用できるもので、しかも、最終消費者に対して製品価格や性能の面で影響が及ぶことがない技術としており、2018年には、業界全体で利用できるように無料で提供していく予定だとしている。