Cadence Design Systemsは11月14日(米国時間)、同社のテストソリューション「Modus」が、高パフォーマンスのARMコアを採用したSoC開発の効率化に向け、ARM Memory Built-In Self Test(MBIST)インタフェースをサポートしたと発表した。

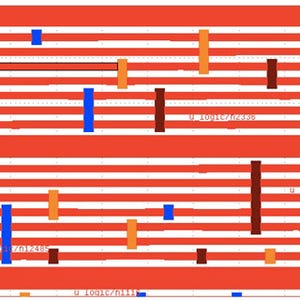

これによりCadenceでは、例えばプログラマブル・メモリ・ビルトイン・セルフテスト(PMBIST)のオプションを提供することが可能となり、単一のMBISTコントローラとバスを経由して複数メモリに対応することを可能とした。

また、MBISTがファンクション動作時のメモリに繋がるクリティカルパスに及ぼす影響を軽減し、より高い品質のat-speedテストを実行することが可能となるとするほか、メモリの物理構造を論理情報にマッピングする機能を提供することで、ミスが発生しやすいマニュアル作業を削減できるようになるとしている。

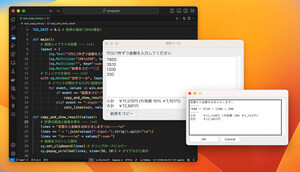

なお、CadenceとARMでは、協業の成果の実証のために、ARM Cortex-A73を用いて、Modusテストソリューションが提供するテストパターン生成(ATPG)および故障診断機能のシリコン上での実証を完了済みであるとしている。