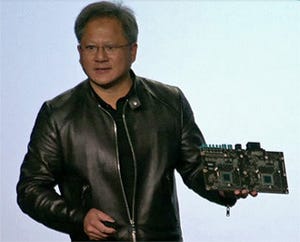

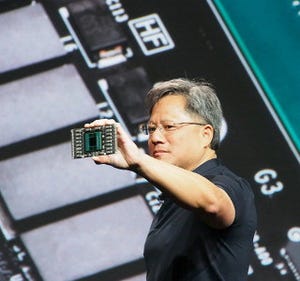

GPU Technology Conference 2016の基調講演を行ったNVIDIA CEOのジェンスン・ファン氏 |

米NVIDIAは5日(現地時間)、開発者向けイベント「GPU Technology Conference」(GTC)にて、Pascalアーキテクチャを採用したデータセンタ向け新GPU「Tesla P100」を発表した。

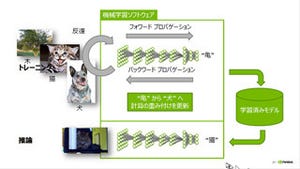

「Tesla P100」は、NVIDIAの新GPUアーキテクチャ「Pascal」をベースとした製品。ディープラーニングとAI向けに開発されたという。製造プロセスは16nm FinFETで、トランジスタ数は153億。ダイサイズは610平方mm。プロセッサ間の接続インタフェースとして「NVLink」をサポート。従来比で5倍となる160GB/sの帯域幅を実現するという。メモリには16GBの第2世代HBM(High Bandwidth Memory)を採用することで、720GB/sのメモリ帯域幅を提供するとしている。

32ビット単精度浮動小数点数(FP32)と64ビット倍精度浮動小数点数(FP64)に加え、新たに16ビット半精度浮動小数点(FP16)をサポートし、それぞれの演算性能はFP32が10.6TFLOPS、FP64が5.3TFLOPS、FP16が21.2TFPLOS。

64基のFP32 CUDAコアと32基のFP64 CUDAコアからなるStreaming Multiprocessorを56基搭載し、CUDAコア数は3,584基(32FP)/1,792基(64FP)。ベースクロックは1,328MHz、ブーストクロックは1,480MHz。TDPは300W。KeplerやMaxwell世代のTeslaとの比較は以下の通り。

| 製品名 | Tesla K40 | Tesla M40 | Tesla P100 |

|---|---|---|---|

| GPUコア | GK110(Kepler) | GM200(Maxwell) | GP100(Pascal) |

| 製造プロセス | 28nm | 28nm | 16nm FinFET |

| トランジスタ数 | 71億個 | 80億個 | 153億個 |

| ダイサイズ | 551平方mm | 601平方mm | 610平方mm |

| SM | 15 | 24 | 56 |

| TPC | 15 | 24 | 28 |

| SMあたりの32FP CUDAコア | 192 | 128 | 64 |

| 32FP CUDAコア合計 | 2880 | 3072 | 3584 |

| SMあたりの64FP CUDAコア | 64 | 4 | 32 |

| 64FP CUDAコア合計 | 960 | 96 | 1792 |

| ベースクロック | 745MHz | 948MHz | 1328MHz |

| ブーストクロック | 810/875MHz | 1114MHz | 1480MHz |

| Texture Units | 240 | 192 | 224 |

| メモリインタフェース | 384-bit GDDR5 | 384-bit GDDR5 | 4096-bit HBM2 |

| メモリ容量 | 12GB | 24GB | 16GB |

| L2キャッシュ | 1.5MB | 3MB | 4MB |

| レジスタファイル | 3840KB | 6144KB | 14336KB |

| TDP | 235W | 250W | 300W |

「Tesla P100」搭載のスーパーコンピュータも投入

また、NVIDIAは8基の「Tesla P100」を搭載したディープラーニング向けのスーパーコンピューター「NVIDIA DGX-1」も合わせて発表。6月に投入する。価格は129,000ドル。なお、大手サーバメーカによる「Tesla P100」搭載システムは2017年第1四半期の提供開始を予定する。