新エネルギー・産業技術総合開発機構(NEDO)は2月1日、同機構のプロジェクトにおいて、65nm世代のシリコントランジスタに混載した4Mビットクラスの新方式磁性体メモリ(STT-MRAM)回路において、3.3nsというキャッシュメモリとして十分に高速なアクセス時間、ならびに揮発性メモリ(SRAM)と比較して消費電力10分の1以下という低消費電力化を実現したと発表した。これは、キャッシュメモリとして世界最高の電力性能であるという。

同成果は、同プロジェクトに参画する東芝と東京大学 情報理工学系研究科 中村宏 教授らの研究グループによるもので、1月31日~2月4日に米サンフランシスコで開催される半導体回路国際会議「ISSCC 2016」において、2月2日(現地時間)に発表される。

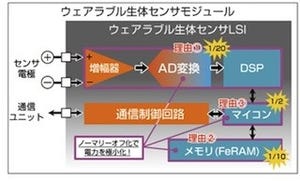

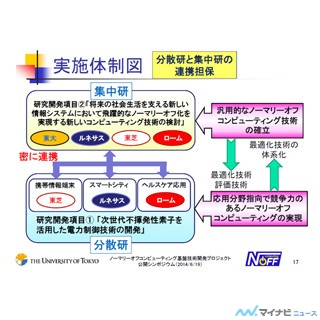

同機構は、不揮発性メモリを利用して、コンピュータの非動作時に積極的に電源をオフして省電力化を図る「ノーマリーオフコンピューティング基盤技術開発」プロジェクトを推進している。コンピュータのキャッシュメモリに使われるSRAMのような高速メモリは揮発性メモリであるため、データの保持を考えると電源オフができない一方で、今までの不揮発性メモリでは高速化が実現できていない。このため同機構は、SRAMに代わる高速で低消費電力の不揮発性磁性体メモリ「MTJ(Magnetic Tunnel Junction)」の開発を続けていたが、メモリ制御回路部が消費する電力が大きいため、不揮発性メモリのみの低消費電力化を実現してもキャッシュメモリ全体としての消費電力は十分に小さくならないという課題があった。

そこで今回、同研究グループは、メモリ制御回路部をノーマリーオフ動作状態に近づけるため、100ns以下で高速に電力遮断・復帰が可能な回路を開発。メモリ動作状態に応じて動作に必要な部分以外は高速で電源遮断できるように改良した。

主な動作モードでの実測値として、キャッシュメモリアクセスの平均待機時間である約30nsよりも短い、最速22nsで電源遮断後からの復帰を確認しているという。また、メモリのデータを一度確認して不要な書き込みを止めることで書き込み動作の消費電力を削減する技術を採用。さらに、電源を遮断できる時間をできるだけ長くするために、メモリアクセスパターンをモニターして、次のアクセスパターンを高い正解率で予測するアルゴリズムを開発。これらの技術により、従来のSRAMと比較して消費電力を10分の1以下にまで削減することに成功した。

同研究グループは今回の成果について、キャッシュメモリを搭載する情報機器に広く適用可能で、幅広い情報機器の消費電力を低減し、社会全体の省エネルギー化が期待されるものであると説明している。