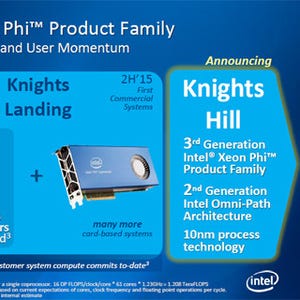

Intelは、米Argonne National Laboratory(ANL)が2018年に稼働を予定しているピーク演算性能180PFlopsの次世代スーパーコンピュータ「Aurora」に搭載される予定である10nmプロセス採用の次世代Xeon Phi「Knights Hill」(開発コード名)の開発が予定通りに進んでいることを明らかにした。

これは、12月10日、同社の日本法人であるインテルが都内で開催したHPC分野のカンファレンス「インテル ソフトウェア・カンファレンス東京」のメディア向けラウンドテーブルにて語られたもの。

|

|

|

|

Argonne National Laboratoryが計画している次世代スパコン「Aurora」には、第3世代Xeon Phi「Knights Hill」が搭載され、ピーク演算性能180PFlopsの実現を目指す |

|

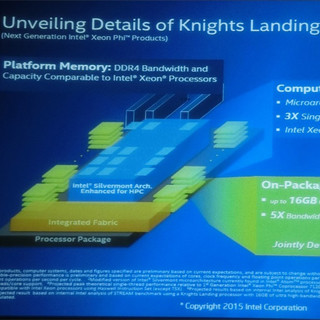

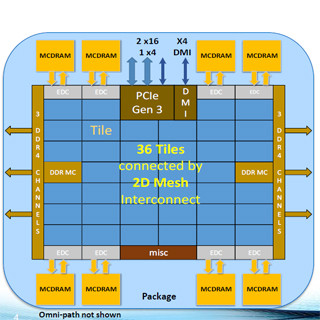

ラウンドテーブルの話題の中心は、第2世代Xeon Phi「Knights Landing」(開発コード名)を核とする「Intel Scalable System Framework(SSF)」であった。これは、プロセッサ、ファブリック、メモリ/ストレージ、ソフトウェアの4つの要素を組み合わせることで、柔軟性のあるHPCの構築を実現しようというもの。ファブリックとしては、第1世代Omni-Pathが採用される。この第1世代Omni-Pathに関しては、2014年にKnights Hillの存在が発表された際に語られたこと以上に新たな点はほぼ見られなかった。

また、Intelは今年、FPGAベンダのAlteraを買収し、同社のFPGAをデータセンター向けに活用していくとアナウンスしている。実際に、MicrosoftはAlteraのFPGAを用いて低消費電力かつ検索エンジン「Bing」の処理高速化を実現する「Catapult」を開発しており、その有用性を証明している。今後、HPCの分野でも同様にFPGAの活用が見込まれることから、その点を、Intelのデータセンター事業本部 エンタープライズ&HPCプラットフォーム事業部 HPCマーケティング&インダストリーデベロップメント ディレクターであるHugo Saleh(ヒューゴ・サレー)氏に確認したところ、すでに同社が2015年6月のISCA 2015でXeon+FPGAを明らかにしているが、「そうした流れはHPCの分野でも考えてもらってよい」とのことで、どういった構成になるかは別として、Xeon+Xeon Phi(コプロセッサ)+FPGA(アクセラレータ)といった構成によるさらなる演算性能の向上と低消費電力化の両立の模索が進められることを示唆した。