キヤノンは2月23日、同社が2015年内の製品化を目指して研究を進めているのナノインプリント半導体製造装置の概要を発表した。

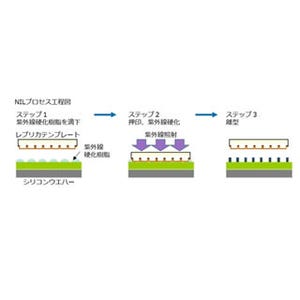

同装置ではマスク(原版)をウエハー上のレジスト(樹脂)に直接押し付けることで、マスクに掘り込まれた回路パターンを忠実に転写できるため、光露光装置に比べ、高解像度で均一性のある回路パターンを描くことができる。また、光露光装置に使用されている光源や大口径レンズ群が不要のため、装置自体をコンパクトにでき、複数代の装置をクラスタ化して設置することで生産性の向上が期待できる。さらに、半導体デバイスの製造コストを大幅に削減できるため、高精細半導体デバイスのCoO(Cost of Ownership)の低減を求める半導体メーカーのニーズに対応することができるとしている。

導入先としては、まずはフラッシュメモリーを製造するメモリーメーカーを予定しているが、将来的にはDRAMやロジック系半導体の生産への適用も視野に入れている。