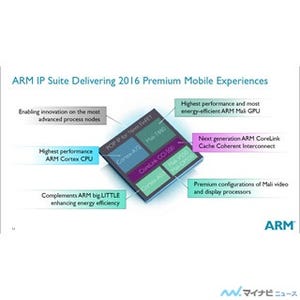

CadenceとARMは2月3日(現地時間)、最新のARM Cortex-A72プロセッサ、ARM Mali-T880 GPU、ARM CoreLink CCI-500キャッシュコヒーレントインターコネクトソリューションを統合した新しいARMプレミアムモバイルIPスイートに対応する、完結したSoC開発環境を発表した。

今回提供されるのは、TSMCの16nm FinFET+をはじめ、最先端の製造プロセスに対応するARM Cortex-A72プロセッサ向けのリファレンスフローである。さらに、このリファレンスフローでは、ARM Cortex-A72プロセッサ、およびARM Mali-T860とT880 GPU向けに最高性能を誇るARM ArtisanフィジカルIPやARM POP IPも利用できるので、プロセッサ性能および消費電力のアグレッシブな目標を達成することが可能になる。また、Candenceの開発環境には、ARMプレミアム モバイルIPスイートに対応するデジタルおよびシステムからシリコンまでの検証ツールやIPも含まれており、複雑なハイエンドのモバイル製品の市場投入時間を短縮することができる。

なお、両社はこの新プロセッサとARMプレミアルモバイルIPスイートに対応するための取り組みにおいて協業した。具体的には、RTL合成から最終サインオフまでの理想的なリファレンスフローを定義することにより、プレミアムモバイル市場における最適なPPAの達成を図った。これにより、Encounter Digital Implementation System、Encounter RTL Compiler、Encounter Conformal製品、Tempus Timing Signoff Solution、Quantus QRC Extraction Solution、Voltus IC Power Integrity Solution、Physical Verification Systemを含むフローはARM社内での仕様により実証済みとなっている。

また、CadenceのPalladium XPシリーズとARM Cortex-A72 Fast Modelsの統合により、従来のエミュレーションのみのソリューションに対してOSの立ち上げ時間を50倍、ハード/ソフトウェア協調開発を10倍の高速化させ、さらにサイクル精度のハードウェア/ソフトウェア同期デバッグのサポートとダイナミック電力解析(DPA)による現実的なソフトウェア負荷のもとでの消費電力と予測性能とのバランスを最適化した。

さらに、自動生成されたテストベンチと多数のARM IPコンフィグレーションをマッチさせるCadenceのInterconnect WorkbenchとARM CoreLink CCI-500との統合を行った。これらのテストベンチを用いて、インターコネクトサブシステムの性能解析をサイクル精度で実行することにより、製品の性能を最適化し市場投入時間を短縮できるとしている。