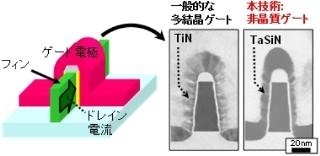

産業技術総合研究所(産総研)は12月16日、LSIの3D積層技術の実現に向けて、新たな多結晶膜形成技術を開発し、N型多結晶ゲルマニウム(Ge)トランジスタの性能を大幅に改善したと発表した。

同成果は、同所 ナノエレクトロニクス研究部門 新材料・機能インテグレーショングループの森貴洋研究員らによるもの。詳細は、12月15~17日に米国サンフランシスコで開催される国際会議「2014 International Electron Devices Meeting(IEDM2014)」にて発表される。

多結晶Geは、広く用いられている多結晶シリコン(Si)に比べ、より低温(500℃以下)で形成できる。そのため、熱的ダメージを与えずに集積回路上にCMOS回路を直接積層でき、3D-LSIの要素技術として有望である。さらに、Ge中の電子や正孔の移動度はSiよりも高いため、高速動作や低電圧動作が期待される。

一方で、集積回路動作にはN型とP型のトランジスタが必要で、多結晶GeのP型トランジスタではすでに通常の単結晶Siトランジスタに迫る十分な性能が得られている。しかし、N型トランジスタの電流駆動力は通常のSiトランジスタよりも1桁以上低いという問題があった。今回開発した技術では、電流駆動力を従来の約10倍に増大できたため、多結晶Ge集積回路の動作速度が実用レベルになると期待され、3D-LSIの実現に貢献することが考えられるとコメントしている。