Keysight Technologiesの日本法人であるキーサイト・テクノロジーは10月9日、DDRバスシミュレータを発表した。

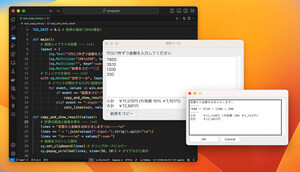

同ツールは、JEDECのDDRメモリバス仕様に準拠しており、正確なビットエラーレート(BER)等高線が作成可能なソフトウェアである。Keysight EEsof EDAのAdvanced Design System(ADS)2014.11のアドオンとして提供され、メモリインタフェースのDQ/DQSに対するアイ確率密度分布とBER等高線をすばやく正確に計算することができる。これまでは、SPICEや畳み込み積分によるチャネルシミュレーションから得られる有限数のビットパターンから、dual-Diracモデルを用いてアイダイアグラムを算出していた。

これに対し、DDRバスシミュレータでは、トランスミッタ、チャネル、レシーバのインパルス応答と理論上は繰り返しがない無限長のビットパターンから、アイダイアグラムを作成する。さらに、JEDECで仕様化されている1E-16等高線を含め、極低BERレベルまでの厳格なDQ/DQSアイ計算を行える。そして、クロストークおよび立ち上がり時間と立ち下がり時間との非対称性を考慮し、等高線やDDR4の受信マスク試験などの表示により、タイミングや電圧のマージンを把握できるようになる。

また、DDRバスシミュレータは、内蔵モデル、IBISモデル、回路モデルの3種類のICモデルに対応しており、どのモデルも回路図で柔軟に組み合わせることができる。内蔵のドライバとレシーバにはそれぞれ、ディエンファシス機能と連続時間リニアイコライゼーション機能が装備されている。