大阪大学(阪大)は12月10日、半導体デバイスの特性を原子レベルから計算できるデバイスシミュレータを開発したと発表した。

同成果は、同大大学院 工学研究科の森伸也准教授、ミリニコフ・ゲナディ特任研究員らによるもの。詳細は、12月9~11日に米国ワシントンD.C.で開催される「International Electron Device Meeting(IEDM)」にて発表される。

半導体は、ナノメートルレベルの微細加工によりデバイスを高性能化・高密度化してきた。しかし、微細化が進むにつれリーク電流や開発コストなどの問題が顕著になってきているのに加え、デバイスサイズの縮小のみによる高性能化が困難になってきた。この限界を打破するため、従来の平面型シリコンMOS型トランジスタに替わる、新しい構造・新しい材料のデバイスが数多く提案されている。多くの選択肢の中から、次世代デバイスとして実用に最も適した構造や材料を効率的に見つけ出すには、その性能を高速で予測できるシミュレータが必要となる。

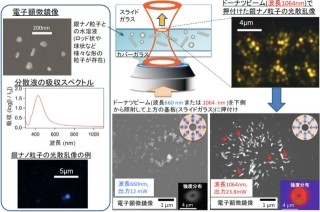

これまでのシミュレーションでは、電子を古典的な粒子と考え、半導体デバイスをシリコン原子の集合体としてではなく、それらを平均化した連続体として扱っていた。しかし、極めて微細な世界では、量子閉じ込め効果やトンネル効果などの量子力学的な効果のため電子を古典的な粒子として考えることが、もはやできなくなっている。さらに、デバイスがナノメートルのサイズになると原子の構造がデバイスの特性に大きな影響を及ぼし、連続体モデルでは説明ができなくなっている。例えば、シリコン原子のわずかな配置の乱れや、1個の不純物の位置の違いにより、作製されたデバイスごとに特性が大きくバラつくことが問題となっている。このように、従来の性能予測シミュレーションでは、ナノメートルサイズの性能予測をすることは極めて困難となっている。

このような中、量子論的な効果を取り入れたデバイスシミュレーション技術の開発が盛んに行われている。しかし、いずれの方法も複雑な計算に多くの時間がかかるため、半導体集積回路の設計に応用することは現在のところ困難となっている。また、回路設計に不可欠なデバイス特性のバラつきを解析するには、原子配置や不純物原子の位置が異なる多数のサンプルに関するシミュレーションを行う必要があり、さらに計算時間が必要となる。そのため、原子論に基づくシミュレーションでのバラつき解析は現実的には不可能と考えられてきた。

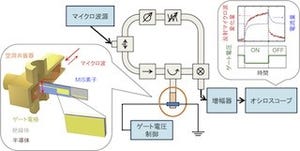

今回の研究では、電気的特性の高速な計算手法の1つであるR行列非平衡グリーン関数法において、デバイスの電気的特性には関与しないエネルギーの電子についての計算を省略し、さらに個々のデバイスにおいて原子配置が乱れる部分は乱れの大きさを表すパラメータ1個のみをバラつき計算に使用することで高速化する、新しい計算モデルを開発した。その結果、原子論的な効果を取り入れたナノデバイスの性能予測計算を、通常のPCで実行できるまで高速化することに成功した。この高速化実現の鍵となる、従来必要だった計算の簡略化に関しては、最終的な計算結果であるデバイスの電気的特性に影響を及ぼさないことが、数学的に保証されている。

今回開発したシミュレータを用いると、直径4nm、ゲート長10nm、全長30nmのシリコンナノワイヤトランジスタ1000個の伝達特性を、通常のPC1台を用いて、数日でシミュレーションできる。この計算には従来1年以上の計算時間が必要となるため、現実的ではないと考えられてきた。さらに、PCを複数台用いる並列計算で、より短時間でバラつき解析が可能であり、また、スーパーコンピュータを利用すれば、さらに多くのサンプルをシミュレーションできる。この高速化により、バラつきを抑制できるデバイス構造・材料の探索や、原子論に基づく電気的特性シミュレータの集積回路設計への応用が進むものと期待される。

今後は、より現実的なナノ構造のデバイスについてのシミュレーションと実験データとの比較を行い、具体的な特性やシミュレーションの正しさを明らかにしていく。また、トランジスタ単体の性能予測だけでなく、複数のトランジスタから構成される電子回路としての性能を予測する回路シミュレータや、電流によるトランジスタ、配線の発熱を予測するシミュレータなどとデータを連携することで、原子レベルから電子回路レベルまでの統合的シミュレータの開発を行う。これらの結果は、さらに微細化していく次世代の半導体集積デバイスの新たな設計指針の構築に寄与するものと期待されるとコメントしている。