AlteraとMicron Technologyは9月4日(米国時間)、AlteraのFPGA「Stratix V」とMicronのハイブリッドメモリキューブ(HMC)の相互接続性を実証するデモを共同で実施したと発表した。

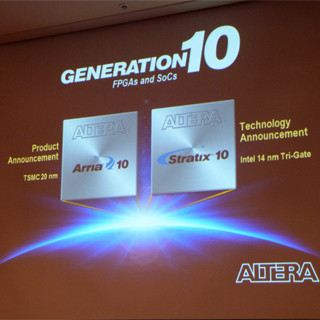

今回の成果により、次世代の通信および高性能コンピュータデザイン向けに、FPGAおよびSoCにHMCを使用する利点を評価できるようになった。デモはFPGA&SoC「Stratix 10」、「Arria 10」を含むAlteraの「Generation 10」ポートフォリオで、HMCのサポートを実証するものとなっている。

HMCは、従来のメモリ技術に課せられた制約を解決するソリューションであり、高いシステム性能を低いビット当たりの消費電力で提供する。DDR3モジュールの最大15倍の帯域幅を、既存の技術に比べて70%低い消費電力、および1/10の実装面積で実現している。HMCの抽象化されたメモリ構造により、基本的な機能を実装するために必要な多くのメモリパラメータの移動が短時間で実施できる。また、メモリの抽象化により、エラー訂正、回復、リフレッシュ、メモリプロセスのバラつきにより生じるその他パラメータの問題を管理する。Micronは年末にもHMCのサンプル出荷を開始し、2014年に量産出荷を開始する予定。

「Stratix V」は現在量産出荷中。「Stratix V」とHMCの相互接続性デモは評価用として提供可能で、「Arria 10」で量産製品をサポートする。早期アクセスプログラムに参加しているユーザーは、開発ソフトウェア「Quartus II」により「Arria 10」の設計を開始している。「Arria 10」の最初のサンプル出荷は2014年上期となる予定。14nm FPGA「Stratix 10」のテストチップは2013年中、「Quartus II」による「Stratix 10」のサポートは2014年に開始される。