東京工業大学(東工大)は、LSIに用いられる一般的なシリコン材料と同じプロセスを利用して、3次元光多層配線を作製し、複数配線層間で毎秒50Gビットの高効率な信号伝送に成功したと発表した。

同成果は、同大大学院 理工学研究科の姜晙炫大学院生、西山伸彦准教授、同大 量子ナノエレクトロニクス研究センターの荒井滋久教授らによるもの。詳細は、9月17日に福岡で開催される「電子情報通信学会ソサイエティ大会」にて発表される。

半導体では、高速な信号を伝送すると配線間で信号混在や、熱エネルギーへの変化が発生し、エネルギー損失が大きくなるという問題を抱えている。そのため、CPUでは動作クロック速度を早くせずになるべく並列処理をすることで、この問題を回避しているが、配線距離が長くなってくれば、クロック速度がそれほど速くなくとも同様の問題が生じてくる。これに対し、最先端のスーパーコンピュータやサーバなどでは、光ファイバを使った光配線への置き換えが進められている。光配線は、コンピュータ内部の部品まで浸透してきており、IntelなどのCPUメーカーも光配線の利用を推進している。将来的には、LSIの中にまで光配線を導入するチップ内光配線も考えられており、その技術として、シリコンフォトニクスが研究されている。特に、CMOS回路上へのダメージなしに光配線を作製できる技術、3次元集積化を実現しながら、複雑な光回路を高密度で集積できる技術などが求められているという。

今回、研究グループでは、LSIと光回路を一括集積できるシリコンを使った光回路技術であるシリコンフォトニクス技術により、光回路を多層集積して高効率に結合し、毎秒50Gビットの高効率な信号伝送を成功した。具体的には、電子ビーム描画技術を中心とする高精度加工技術、低損失アモルファスシリコンの成膜技術、および半導体レーザにおける回折格子設計技術などを利用している。

一般的なシリコンフォトニクス技術による光回路では、結晶シリコンを用いることが多い。この場合、LSIの基本回路であるCMOS回路の耐熱温度である400℃を超えるプロセスが必要となるため、電子回路の上に光回路を集積することは困難である。これを解決するため、300℃程度のプロセス温度で作製できるアモルファスシリコンを導入し、回路を構成することにより電子回路上に光回路を集積できるようにした。それを複数回積み重ねることで、多層光回路を作製することができる。しかし、これまで層間を高効率に結合する技術がなく、独立にしか動作させることができなかった。一方で、層間距離を短くして結合する技術が提案されていたが、結合部以外でも結合が起きやすいなどの問題があった。

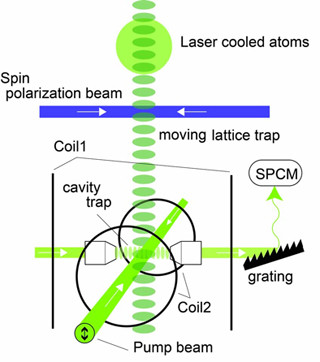

そこで、結合部に回折格子を用いて、信号の進行方向を横方向(層内)から縦方向に変化させることにより、信号を結合させた。同方式は、長い層間距離を容易に伝送できる特徴を持っている。また、これまでの研究により、上下均等に信号が放出される問題が指摘されていたが、回折格子の下部や上部に金属反射ミラーを導入することにより、信号を必要な方向にだけ伝播するようにすることで、80%以上の信号結合効率を実現した。この構造を作製するためのプロセスは、一般的にCMOS回路を作製する際に使われるプロセスと互換性があり、電子回路と今回の構造の集積は容易であるとしている。

|

|

|

|

図1 結合部の構造図 |

図2 毎秒50Gビット信号伝送波形。結合部を含む多層配線の1層目から、2層目に毎秒50Gビットの信号を伝送した場合のオリジナル信号波形(上)と伝送後の信号波形(下)。信号に変化が見られず、劣化が起こっていないことを示している |

同技術が最先端LSIに導入されることによって、電子回路の直近まで光を導入することができるようになるため、現在の配線における信号伝送の速度制限を克服できる可能性がある。その結果、逆スケーリング則とも呼ばれる電子回路微細化に伴う配線遅延がなくなるため、微細化が進んでも、頭打ちすることなくLSIの性能向上が期待できるとコメントしている。