東京工業大学(東工大)は2月15日、集積回路内において注入同期する発振器を周波数補償ループから分け二重ループ構造とすることで、回路内における注入同期現象の安定化に成功したことを発表した。

同成果は同大大学院理工学研究科の松澤明教授、同 岡田健一 准教授らの研究グループによるもの。詳細は2月17日より米国サンフランシスコにて開催されている半導体の国際会議「ISSCC 2013(国際固体回路国際会議)」にて現地時間2月19日に発表される予定。

注入同期現象は、17世紀に壁掛け時計の振り子間の同期現象として発見されたが、集積回路中でも発生することが知られており、回路内に複数の発振器を配置すると、他方がもう一方の周波数につられて誤った周波数で発振を起こすといった誤作動の要因として知られている。

一般的に集積回路は、高いクロック精度を実現できる水晶発振器を用いて、基準クロック信号を発振。その周波数をPLL回路を用いてN倍に増幅することで各回路で求めるクロック信号を提供している。

所望するクロック信号を得る際には、クロックの純度を表すジッタ特性が良好である事、低消費電力ならびに小さな回路面積、そして温度や電源の変動などに対して安定して動作することが重要となるが、従来のクロック生成回路ではジッタと消費電力はトレードオフの関係にあり、ジッタ特性を改善するためには消費電力が増加してしまうという課題があった。

こうした課題に対し、注入同期現象をクロック生成に応用すると、位相雑音特性が電圧制御発振器ではなく、水晶発振器により決まるため、低消費電力を維持したまま位相雑音特性を改善することが可能であるとされていた。しかし、注入同期現象では温度や電源変動に対して安定して動作させることができないという課題があり、実用化への課題となっていたという。

具体的には、注入同期現象を用いたPLLでは、水晶発振器からの低ジッタの基準信号を注入することで、PLL出力クロックの低ジッタ化が可能だが、位相の同期はできるものの周波数の同期ができないため、電圧制御発振器は、あらかじめ所望周波数付近で発振している必要があり、/N分周器、PFD、CP、LPFからなるループによりあらかじめ周波数補償を行う必要がある。しかし、一度動作を開始した場合、注入同期により位相が固定されることとなり、/N分配器に入力される周波数は一定となるため、周波数補償ループは動作ができなくなるため、時間の経過による周辺温度や電源電圧の変化により、注入同期による同期がはずれ、誤った周波数のクロックを出力する状態になるというものだ。

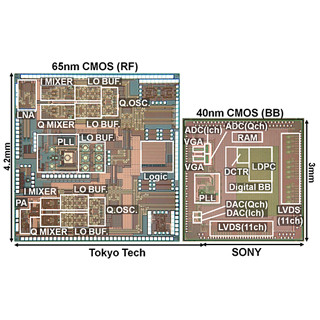

そこで今回、研究グループは主発振器を注入同期し、補助発振器により周波数補償を行う二重ループ構成を採用することで、補助発振器が温度や電源変動に対して追随し、安定した動作を実現できるような回路構成を考案。実際に65nm CMOSプロセスで試作したクロック生成回路では、0.022mm2の面積でループ部を完全なデジタル回路構成とし、2つの発振器間の周波数オフセットを校正したほか、補助ループを間欠動作させることで消費電力の抑制を達成したという。

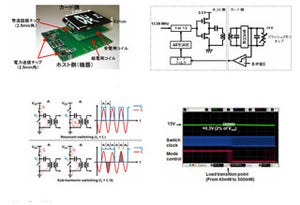

またジッタ特性は、従来型の注入同期PLLの場合、35℃と65℃付近でジッタが増大し、正しい周波数のクロックが出力できなくなったが、新型PLLの場合、温度変化に対しても安定して低ジッタ特性を保つことができることが確認されたという。例えば同試作回路は、40MHzから300MHzの基準信号に対し、0.5GHzから1.6GHzのクロック出力が可能だが、1.2GHz出力時で0.97mWの消費電力、ジッタは0.7psであったという。

なお、研究グループでは、今回の成果は従来困難であった集積回路内部での注入同期現象の安定化を可能とするものであり、従来のPLLを置き換えることで回路の小型化、低消費電力化、低ジッタ化が可能となり、無線機器の小型・低消費電力化やMPU/LSIなどの低消費電力化・高速化・小型低価格化などへの道が開かれたと説明している。