テクトロニクスは12月19日、JEDECのDDR4、DDR3L、LPDDR3規格に対し、電気バリデーションおよび適合性テストのフルサポートを追加したと発表した。

JEDECから発行されるメモリ規格の高速化、低電力消費化が進むにつれ、デバッグや検証の問題も増えている。例えば、新しい規格における高速のリード/ライトアクセスと低電圧動作では、テストフィクスチャからの優れた信号忠実度が必要になる。DDR4では、可変VRef、アイマスク、ジッタを含む、複雑な新規テストが発表されている。これに対し、DDRの全ての世代の規格をサポートするオシロスコープベースのJEDECコンフォーマンスソリューションにより、JEDEC規格テストの迅速なPHY検証を可能にするという。

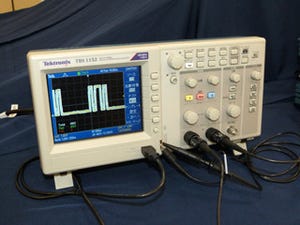

同社は、DDRA解析ソフトウェアで次世代メモリ規格の統合サポートを提供し、新しい規格のメモリインタフェースの電気適合性試験とデバッグをサポートする。同ソフトは「MSO/DSA/DPO70000」シリーズ、「DPO7000」シリーズ、「MSO/DPO5000」シリーズの各オシロスコープにて利用可能で、DDR規格の第1世代から最新の世代の規格までサポートすることが可能だ。DDRAソフトウェアを使用することでセットアップ、テストが自動化できるため、メモリ規格への適合性を確実なものにすることができるほか、メモリシステムが適合性試験でフェイルになった場合でも、素早くデバッグモードに切り替え、同社のオシロスコープのビジュアルトリガなどのツールで特定のイベントを特定し、DPOJETジッタ/アイダイアグラム解析ソフトウェアでより詳細な解析が可能になる。

さらに、DDR4、LPDDR3で利用する新しいインターポーザ(DIMM、PoP、エンベデッド)を含んだ、すべてのメモリ技術をカバーする豊富なプロービングソリューションも提供される。これら新しいインターポーザのコントロールされたインピーダンスとマッチングのとれたトレース長、オシロスコープによるディエンベデッドフィルタの組み合わせにより、正確な信号再生が可能となると同社では説明する。

また、アップデートに加え、ロジックアナライザ「TLA」7000シリーズによる多チャネルメモリシステムの検証、ミクスドシグナルオシロスコープ「MSO70000」シリーズによるロジック、アナログ両方の信号取り込みなど、詳細なメモリテストサポートも提供される。

なお、新しいDDR4とLPDD3用のインターポーザとDDRAソフトウェアのアップデートは2013年第1四半期より提供される予定。