富士通セミコンダクター(FSL)は10月16日、ARM Cortex-A9デュアルコアプロセッサおよび各種インタフェースを1チップ化したInterface Bridge SoC「MB86E631」を開発したと発表した。

スマートフォンやタブレットの普及により、携帯端末でのTV視聴を可能とするWi-Fi TVチューナ製品が販売されている。このような製品にはビデオフォーマットや解像度変換を行うトランスコーダLSIやWi-Fiモジュールが搭載されているが、これらを制御するCPUとして、レコーダ用のマルチデコーダLSIやネットワーク製品用の通信プロセッサでは性能が過剰であり、マイコンなどの廉価なCPUでは性能が不足するという問題があった。

一方、レコーダーや録画機能付きTVなどの機器メーカーからは、接続される様々な装置に対応する各種インタフェースを制御する機能を持ったCPUが求められていた。

これらのニーズに対応するため開発された同製品は、CPUコアにARM Cortex-A9デュアルコアプロセッサ(~500MHz動作)を採用し、USB2.0/3.0、Serial ATA、PCI Express、Ethernet MAC、TSなど、合計10種類のインタフェースを1チップに集積した。トランスコーダLSIとの組み合わせで実現するWi-Fi TV チューナ用SoCとしての利用だけでなく、複数のインタフェース制御が必要となる多チューナー搭載製品などのインタフェース制御用CPUにも利用することが可能。加えて、映像の配信や録画を行う製品に限らず、マイコン以上の性能および各種インタフェースを必要とする新たな市場にも対応するため、展開していく方針。

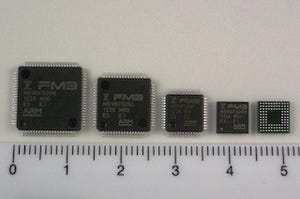

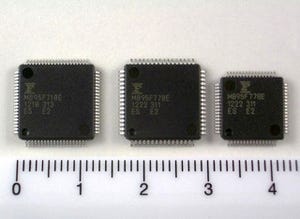

なお、パッケージは16mm角の426ピンFBGA(ボールピッチ0.65mm)。2012年12月下旬よりサンプル出荷開始する。販売目標は月産10万個。