東京工業大学(東工大)とソニーは2月20日、6.3Gbpsのミリ波無線データ伝送を実現する低消費電力の高周波(RF) LSIおよびベースバンド(BB) LSIを共同開発したことを発表した。同技術が実用化すると、モバイル機器間で高速にデータを送受信したり、高画質な映像を非圧縮で送りながら視聴したりすることが可能になるという。開発成果の詳細については、2012年2月19日から米国サンフランシスコにて開催されている「国際固体素子回路会議(ISSCC 2012)」で発表される。

共同開発を進めるにあたっては、ソニーがBB LSIのデジタル部の設計とチップ全体の開発を担当し、東工大がRF LSIとBB LSIのアナログ部の設計を担当した。

ソニーが開発を担当した高効率・高信頼性のレート14/15 Low-Density Parity-Check (LDPC)誤り訂正符号によって、誤り訂正を行うために必要となる付加データ量そのものを削減、ビット当たり消費電力11.8pJ/bit(6.3Gbps動作時 74mW)でLDPC復号処理を実現した。このLDPC符号は60GHz帯ミリ波標準 IEEE 802.15.3cへ提案し採用されている。

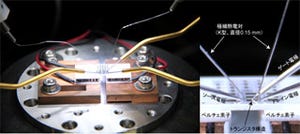

一方、東工大の松澤昭教授と岡田健一准教授らの研究グループが開発したRF LSIは、60GHz帯ミリ波ダイレクトコンバージョン無線機で、高速な無線通信を可能とする16 Quadrature Amplitude Modulation(16QAM)に、各種60GHz帯無線標準規格において規定されているすべての周波数チャネルで対応することを可能としたもの。

これまで東工大では、注入同期型局部発振器の開発によって、周波数チャネル2チャネルまでの対応を実現していたが、今回、開発されたRF LSIでは注入同期型局部発振器を独自の折り返し型構造にすることで、周波数チャネル全4チャネルへの対応を可能とした。

また、BB LSIに搭載したアナログデジタル変換器では、変換誤差を増加させずに比較器を簡略化できる技術を開発することにより、60GHz帯無線機に搭載されたアナログデジタル変換器として消費電力12mW(2.3G samples/s 動作時)を実現している。