東北大学とNECの研究グループは、電子の性質であるマイナス電荷や微細な磁石であるスピンを利用したスピントロニクス技術とシリコンCMOS技術を組み合わせて、600MHzで動作する不揮発性論理回路を開発したことを発表した。同成果は、東北大 省エネルギー・スピントロニクス集積化システムセンターの遠藤哲郎教授と大野英男教授のグループとNECの研究チームによるもので、12月5日から7日まで米ワシントンDCにて開催されていた半導体デバイス技術の国際学会「2011 IEEE International Electron Device Meeting(IEDM 2011)」にて発表した。

プロセスの微細化により1つのシステムを1チップで実現することができるようになってきたが、システムLSI上のトランジスタの個数が増加することで漏れ電力が増大し、待機時電力の増加が課題となっている。そのため、論理回路中のデータ記憶部を不揮発性化し、待機時において電源を遮断する研究開発が進められている。

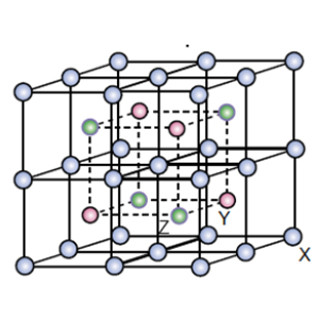

論理回路中の不揮発性記憶デバイスには、CMOS回路との整合性、微細化による性能向上、高速書き込み・読み出し性、及び書き込み回数耐性などから、スピン注入磁化反転型磁気トンネル接合(Magnetic Tunnel Junction:MTJ)デバイスが最適なものと考えられているが、MTJデバイスは高速にスイッチングする時に大きな電流を必要とするため、動作周波数を抑えなければならず、CMOSによる論理集積回路の最高動作周波数をMTJ不揮発性論理集積回路で達成することは困難であった。また、従来のMTJ不揮発性論理集積回路では動作周波数を上げるとスイッチングに失敗する確率(エラー率)が高くなるため、論理回路を不揮発性化して低消費電力のシステムLSIを実現する上での課題となっていた。

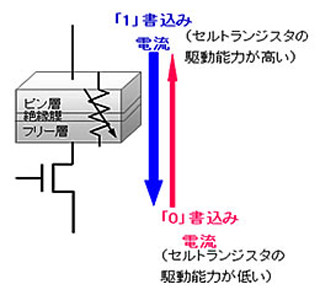

今回、研究グループでは、MTJデバイスのスイッチングが、ある遮断周波数fc以上の周波数では起こらず、かつそのfcは MTJスイッチングのインキュベーション時間の逆数に対応することを発見した。これに基づき、MTJデバイスのスイッチングが行われず、CMOSラッチのみを反転させるローパス・フィルタ機能を持つMTJ/CMOS混成回路を開発したという。

この回路は同期型論理集積回路の基本構成単位の1つであるフリップフロップの要素回路(ラッチ回路)で、NECが回路の微細スピントロニクスデバイス部分を標準シリコンCMOS回路上に作製し、東北大学が原理動作を実証した。

回路は、周波数がfcより大きいときに外部入力されたデータはCMOSラッチ部に記憶し、MTJデバイスのスイッチングを実行しない。周波数の低下とともにスイッチングが行われるため、スイッチングに高い電流を必要とせず、またスイッチング後は電源を遮断できるため、LSIの低消費電力化が可能となるという。また、一般のCMOS LSIと同等の速度であり、MTJ/CMOS混成回路としては世界最高速となる周波数600MHzでの動作を確認したとしており、これにより、低消費電力、高速動作、低エラー率を同時に達成したこととなった。

さらに、MTJデバイスのスイッチング切り替えを制御する回路が不要となるため、その分の回路によるチップ面積や消費電力のオーバーヘッドはなく、簡単に設計が出来るとのことで、これによりシステムLSIのさらなる低消費電力化が前進することになると研究グループでは説明している。