NECエレクトロニクスは、オンチップ配線に匹敵する微細インターポーザ配線によりチップ間接続を実現できる、SiP技術を開発したことを明らかにした。また、東京工業大学と共同で同配線の伝送特性を実測、10GHz以上の高速伝送性能が得られることを確認したという。

同パッケージ技術は、同社のSiP技術「SMAFTITM」を発展させたもので、Siウェハ上に形成するフィードスルーインターポーザ(FTI)の多層化を実現したもの。これにより、パッケージ内の配線引き回し性能が向上し、自由度の高いパッケージ設計が可能となった。

多層化のポイントは、樹脂CMPによる配線体の平坦化処理で、今回開発したCMP技術では5μm以上の樹脂段差を0.5μm以内に抑えることが可能だとしており、これにより、チップと多層FTIを50μmピッチのマイクロバンプで接合することができるようになったという。また、伝送線路の形成も容易になったことで、信号伝送特性が向上したという。

同工法の特徴の1つは、Siウェハ上のFTIに対してLSIチップを接合することにあり、TSV(Si貫通電極)を用いた三次元積層にも対応する。これまでは、チップ積層する際には、チップ接合と接合部の樹脂封止に長時間を要し、コストが高いのが課題であったが、今回開発した工法ではCuピラーバンプを形成したデバイスウェハ側に、あらかじめ樹脂を供給することで、鉛フリーでのはんだ接続と樹脂封止を同時に行うことで工程を短縮。これにより、従来のフリップチップパッケージでは出来なかった数千ピン以上の電気接続を、低コストで行うことが可能になった。

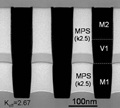

今回新たに開発されたFTIは、層間厚5μmのポリイミド樹脂内に形成された、最小線幅10μm、厚さ5μmの多層Cu配線(スーパーコネクト)により構成されている。このようなスーパーコネクトは、従来のインターポーザー配線より微細であると同時に、オンチップ配線より容量・抵抗が小さく、高速伝送に優れている。東工大と共同で多層FTIの最適化設計を行ったことで、10GHz以上の伝送性能が得られることを実験的に確認。これにより、SiP内のチップ間伝送、チップからパッケージ外部への出力のいずれにおいても高速伝送が可能となり、SiPであってもSoC並みの高集積化と高速動作を行うことができることが実証された。

同社では、同技術を用いることで、ロボットや自動車走行支援システムのような分野に対したシステムLSIの設計、製造を大幅に効率化し、ユーザーの快適な装置利用を実現するものとして、今後とも積極的に研究、開発活動を継続し、製品化を進めていく計画であるとしている。