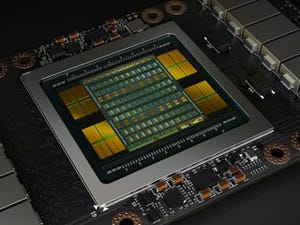

V100 GPUの構造

次の図は、V100 GPUの構成図で、全部で84個のSM(Streaming Multiprocessor)が描かれている。SMは独立したプログラムを実行できる単位で、マルチコアCPUのCPUコアに相当する。

なお、V100チップには84個のSMがあるが、4個は歩留まり改善のための冗長分で、V100チップの仕様では、使用できるSMは80個ということになっている。P100では56SMであったので、SM数は1.43倍になっている。

また、チップレベルの図で目に付くのはNVlinkのリンク数が4から6に増えていることである。なお、NVLinkのデータ伝送速度は、P100では20GbpsであったがV100では25Gbpsに引き上げられている。

|

|

|

V100 GPUは84個のSMを集積している。そして、図の上辺にはホストインタフェースのPCI Express、左右の辺に合計8個のメモリインタフェースを持ち、4個のHBM2が接続される。下辺には6チャネルのNVLinkが描かれている |

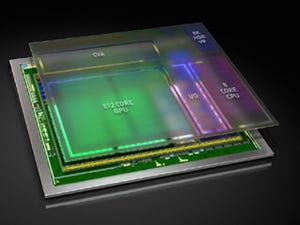

しかし、Voltaの大変更は、その次のSMの構成にある。次の図のように、SMは4つのブロックに分かれており、それぞれがL0命令キャッシュ、ワープスケジューラ、ディスパッチユニットを持っている。P100ではSMは2つのブロックであったので、命令の発行系が2倍に強化されている。

そして、演算ユニットは、FP64が4ブロック×8個、FP32が4ブロック×16個、LD/STが4ブロック×8個SFUが4ブロック×1個描かれている。SMあたりのFP64とFP32の総数はP100と同じであるが、LD/STはP100に比べて2倍の32個となっている。一方、SFUは16個から4個に減っているが大きな箱が描かれているので、V100のSFUは性能が高くなっているのかもしれない。

VoltaのSMでの注目は、かなり大きな面積を占める4ブロック×2個のTensorコアである。チップ全体で640個のTensorコアが搭載され、ディープラーニングでは120TeraOps/sという性能を叩き出す。92TeraOps/sのGoogleのTPUを上回る性能である。そして、TPUは8ビット整数で計算しているので推論専用であるが、VoltaはFP16で計算しており学習にも使用できるという点が異なる。

Voltaでは、従来はFP32と共通のCUDAコアに入っていた整数演算がINT32として独立した。これにより、FP32の演算を行いながら、並行してINTでアドレス計算を行うという使い方ができるようになっている。また、SMあたりのLD/STが32個となり、P100と比べると2倍のLD/STユニットを持っている。

|

|

|

SMは大きく4分割されており、それぞれがワープスケジューラ、ディスパッチユニットとレジスタファイルと演算器群を持っている。演算器はINTとTensor Coreが新設されている。そして、SM全体で128KBのL1キャッシュ/シェアードメモリと4つのテクスチャユニットがある |

新設計のTensorコア

注目はTensorコアである。図では4列16個の小さな箱が並んでいるが、Tensorコアは、64個のFP16の積和演算器を備えている。Tensorコアは、4×4の行列AとBを入力として、この2つの行列の積を計算し、それに4×4の行列Cを加えるという演算を行う。このTensor演算の良いところは、A、Bはそれぞれ16個のデータであり、通常の積や和の演算であれば16演算、積和演算でも32演算しかできないが、Tensor演算では64積和=128演算を行う事ができ、データ1個当たり8演算が行えるという点である。そして、入力はFP16であるので、8個のレジスタからデータを読めば良い。これは8個のFP32の積、あるいは和を計算する場合と同じである。

ここで、行列AとBはFP16、行列Cと加算結果DはFP16、あるいはFP32とすることができる。Tensor演算には4×4×4回の積和演算が必要であり、Tensorコアはこの64演算を毎サイクル行うことができるユニットである。1回の計算には64積和演算が含まれ、V100チップにはTensorコアが640個あるので、81920演算/サイクルであり、これを1455MHzのブーストクロックで行えば119.1936TeraOps/sということになり、これを丸めて120TeraOps/sと称している。

次の図はTensorコアの演算を説明するもので、FP16同士の積の計算はIEEE754のフル精度で行い、それらの積をFP32で加算し、最終的にはFP32で結果を出している。CとDをFP16にするのは簡単で、C入力がFP16の場合はFP32に拡張し、D出力の丸め位置をFP16にするだけで良い。

次の棒グラフは、P100とV100の行列同士の積の計算性能を比較したものである。P100の性能を1に正規化して、V100の性能を赤い棒で表わしている。2つあるグラフの左側はFP32で計算を行った場合で、行列のサイズで多少のデコボコはあるが、おおむね、FP32コアの数に比例する1.5倍程度の性能になっている。

しかし、右側の行列積の入力はFP16で、加算はFP32というTensorコアが使える場合は、行列サイズ2048の場合で9.3倍という性能となっている。つまり、Tensorコアが使える場合は、FP32で計算するより6倍くらい高い性能が得られる。

次の表に、Tesla K20、M40、P100と今回のV100の諸元の一覧表を示す。

なお、GoogleのTPUは行列積の入力はINT8である。この精度でも推論には使えるが、学習に対しては精度不足ということで、NVIDIAは行列積の入力をFP16、加算を繰り返す部分はFP32が使えるようにして学習にも使える仕様にしたと思われる。SMの構成図の各演算コアの面積がどの程度正しいのかは分からないが、Tensorコアの個々の箱はFP32の箱より小さく描かれており、ある程度は面積比例で描かれているとすると、Tensorコアはかなり大きな面積を占めていると見られる。

(次回は5月23日に掲載します)