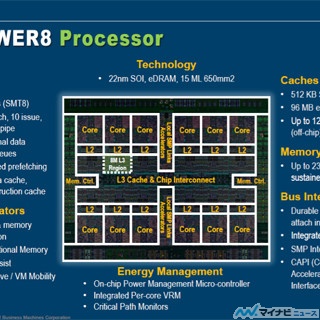

eDRAMやキャッシュ間のバスなども強化されたPOWER8

POWER8ではeDRAMで作られた96MBのL3キャッシュを搭載する。このeDRAMのL3キャッシュはPOWER7でも存在したが、容量は32MBであった。しかし、POWER7+では80MBに増強されており、それと比較するとPOWER8では20%の増加ということになる。

キャッシュ間のバスも強化されており、L2キャッシュからコアへの読み込みバスの幅は256バイト幅、L3キャッシュからL2キャッシュへの読み込みとL4キャッシュからL3キャッシュへの読み込みバスの幅は128バイトとなっている。また、書き込みバス幅はコアからL2キャッシュは64バイト幅、L2キャッシュからL3キャッシュは128バイト幅、L3キャッシュからL4キャッシュは64バイト幅となっている。そして、コアクロックを4GHzとした場合、12コア全体では、L2キャッシュの総バンド幅は4TB/s、L3キャッシュの総バンド幅は3TB/sに達する。

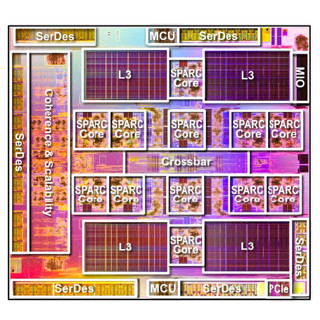

DRAMを接続するメモリバッファチップ「Centaur」

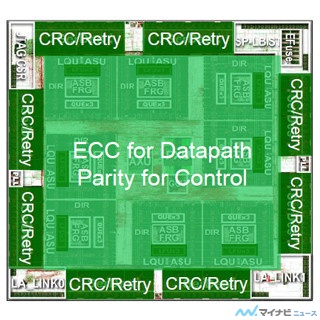

また、POWER8では、 「Centaur(英語ではセンターであるが、日本語ではケンタウルス)」と呼ぶメモリバッファチップを経由してメインメモリのDRAMを接続している。POWER8では8個のCentaurチップがPOWER8チップに接続できる。CentaurチップとDRAMの間のピークバンド幅は410GB/sで、これは富士通やOracleのサーバの約4倍のバンド幅である。結果としてPOWER8は、実効で230GB/sという強力なメモリバンド幅をもつモンスターとなっている。

メインメモリであるが、IBMは、CentaurチップとDRAMチップを搭載した専用のメモリボードを作っている。カードエッジタイプのコネクタは接触不良を起こし易いので、IBMのハイエンドサーバでは使用していない。また、専用のボードであるので、CentaurチップとDRAMをボード上で接続することにより、4ストリングのDRAMを接続して、高いバンド幅が得られるというメリットがある。

そして、Centaurチップは、CPUチップと同じ22nm SOIプロセスで作られており、DRAMアクセスが効率的となるようにするスケジューラやメモリ周りのRAS機能などと合わせて、16MBのキャッシュが搭載されている。

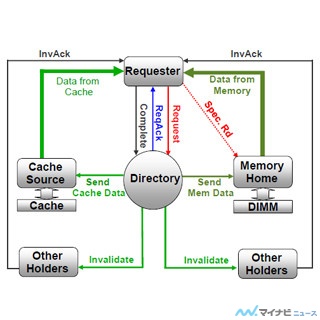

Centaurチップ8個で合計128MBのL4キャッシュが存在することになる。L3キャッシュまでは、どのメモリアドレスのデータでも格納するという普通のキャッシュであるが、このL4キャッシュは、そのCentaurチップに接続されているDRAMのデータだけを格納するメモリキャッシュとなっている。

通常のインクルージョンキャッシュで128MBであれば、96MBのL3キャッシュと重複するエントリが3/4となり、ムダになってしまう。しかし、メモリキャッシュとしてプリフェッチを効かせれば、それなりの効果はあるのであろう。なお、このL4キャッシュはPOWER7/7+には存在しないものである。

POWER7までは、IOの接続はGXバスと呼ぶ独自のバスを使用していたが、PCI Express 3.0になって、性能的に独自バスを使うメリットが無くなったという。このため、POWER8ではPCI Express 3.0を、直接サポートする構造に変わった。

また、POWER8では、CAPI(Coherence Attach Processor Interface)という機構が追加された。

通常、PCI Expressに接続されるGPUなどのアクセラレータのメモリはCPU側のメインメモリとは独立でキャッシュコヒーレンシは維持されない。このため、プログラミングが難しくなるという面がある。これに対して、CAPIはPCI Expressに接続されたアクセラレータのメモリのキャッシュコヒーレンシを維持しようというメカニズムである。

そのためには、アクセラレータ側のメモリにスヌープなどのキャッシュコヒーレンシを維持するメカニズムが必要になる。しかし、通常のGPUなどはこのような機構を持っていないので、CPUチップの中にこの機構を用意しておいてやろうというのがCAPIである。

アクセラレータ側にPSLという機構が必要となるので、既存のPCI ExpressのGPUが使えるというわけではないようであるが、この機能を実装したアクセラレータなら、マルチコアの新たなコアのように共通メモリで動作することが可能になるというメカニズムである。

原理的には良いメカニズムであると思うが、このようなIBM使用のキャッシュコヒーレンシ機能をサポートするアクセラレータがどの程度一般化するかが鍵ではないかと思われる。

そして性能であるが、POWER7+を1.0とすると、POWER8はチップあたり、メモリバンド幅で2.5倍の性能を持ち、ビジネスアプリやJAVA、整数、浮動小数点ベンチマークなどで2.2~2.7倍程度の性能となっている。