そして、Celerityチップは、第3階層として特化した2値化ニューラルネットワーク層を持っている。

2値化ニューラルネットワーク層は、1つの固定小数点の畳み込みネットワーク層、6つの2値畳み込み層、2つのフルコネクト層と各層にバッチ正規化計算層を持っている。2値ニューラルネットワーク層は、0.356mm2であり、625MHzクロックで動作する。

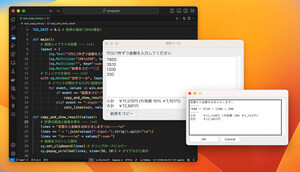

測定を行ったネットワークは、次の図のような構造になっている。汎用処理階層だけで処理を行うと、目標の200倍の時間が掛かってしまう。2値化畳み込み層が97%の計算を行っているが、この層のハードウェア化だけでは、まだ、目標の5倍の処理時間が掛かってしまう。3つのすべての層を使うことで、初めて目標とする性能が得られている。

|

|

|

汎用処理階層だけでは、目標の200倍の時間がかかる。2値化ニューラルネット計算が全体の97%の演算を占めるが、この部分を専用処理階層に割り当てても、目標の5倍の時間がかかる。3階層すべてを使って、目標を達成できる |

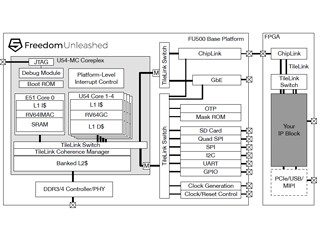

2値ニューラルネットワークのアクセラレーション層は、次の図のような構造になっている。

|

|

|

BNN特化処理階層は、メモリにアクセスするユニット、バッファユニットとコンピュートユニットが含まれる。コンピュートユニットは固定小数点の畳み込み演算、バイナリの畳み込み演算、バイナリのフルコネクト演算を計算するサブユニットを持っている |

高並列処理層は汎用処理階層のRocketコアのキャッシュを使って重みデータを読むこともできるが、それではチップ外へのアクセスが発生して効率が悪い。そのため、高並列処理階層のコアのデータメモリに重みを格納することにした。

汎用処理階層だけを使用した場合、1イメージの処理時間は4,024msであるが、これに特化処理階層を加えると、処理時間は5.3msとなり、性能は約700倍となる。さらに、高並列処理階層も使うと、処理時間は3.3msとなり、汎用処理階層だけの場合に比べて約1,220倍の性能となる。

|

|

|

汎用処理階層だけの場合は1つのイメージの処理に4,024ms掛かるが、特化処理階層を加えると5.8msに短縮され、さらに高並列処理階層を加えると3.3msに短縮される。これは汎用処理階層だけの場合の1220倍の性能である |

16nmプロセスを使うCelerityチップは、全米に散らばった4つの大学のキャンパスの大学院の学生が協力して、9か月で130万ドルの予算で開発した。これを可能にしたのは、再利用とモジュール化、そして自動化設計である。

再利用という点では、オープンソースやサードパーティーのIPを利用し、拡張可能なパラメタ化された設計を利用した。モジュール化という点では設計の最初の段階でインタフェースを決めて分担して設計を行った。自動化という点では、実装とテストフローの大枠を決め、設計の自動化を推し進めた。

再利用という点では、Basejumpというオープンソースの変形可能なハードウェア部品を使用した。プロセサはオープンソース命令セットであるRISC-Vを採用し、RocketコアやVanillaコアを利用した。そして、RoCCというオープンソースのオンチップのインタコネクトを使った。

拡張可能な設計とするため、BSG Manycoreなどを使用している。また、ARMのスタンダードセルやI/Oセルなどを利用している。

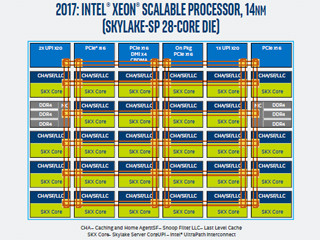

|

|

|

再利用という点では、Basejumpというオープンソースの変形可能なハードウェア部品を利用した。プロセサコアはRISC-VのRocketコアとVanillaコアを利用している。そのほかにRoCCやBSG Manycore、ARMのスタンダードセル、I/Oセルなどを使っている |

迅速な設計という点で、部品レベルで設計を最適化し、ツールの処理時間を短くするため階層化設計を行った。また、詳細な中身を知らなくても利用できるブラックボックス設計を行った。

インタフェースを初期に決めるという点では、RoCCやBasejumpの使用でインタフェースの決定を早め、できるだけレーテンシに依存しないインタフェースを使った。

設計の自動化という点では、実装とテストのフローを抽象化して、色々な設計に適用できるようにした。また、確認済みのIPコンポーネントを利用し、インテグレーションのテストだけで済むようにした。

設計の自動化についてはハイレベル合成ツールを使用した。また、アナログ設計が行われていた部分についてもディジタル設計のフローを使うようにした。

結論であるが、このプロジェクトで、プログラマビリティを犠牲にすることなく、性能を向上させエネルギー効率を高める多階層のアクセラレータファブリックのアーキテクチャを確立した。

Celerityチップは、このアーキテクチャを実証するケーススタディである。

再利用、モジュール化、自動化で、大学院生だけのグループで511個のRISC-Vコアと2値化ニューラルネット処理のアクセラレータを搭載する16nm ASICを9か月で開発した。