Samsung Electronicsは、これまで非メモリ事業はすべてシステムLSI事業部が担当し、ファウンドリ事業は自社内の家電製品向けシステムLSI事業の副業のような扱いとしてきた。しかし、将来的なファウンドリ事業の強化に向け、2017年5月にファウンドリ事業部をシステムLSI事業から分離独立させた。これにより、同社の半導体事業は、メモリ事業部、システムLSI事業部、そしてファウンドリ事業部の3事業部体制に変更され、ファウンドリ事業に注力していくことを明確化。その流れを受け、日本でも、顧客にもっと近い立場で接することを目的に9月15日に、開発者向け技術シンポジウム「SAMSUNG FOUNDRY FORUM (SFF) JAPAN 2017」を開催した。

|

|

|

図1 Samsung Foundry Forum Japan 2017の会場風景。参加者にあいさつするSamsung Electronicsのファウンドリ事業担当EVP兼ゼネラルマネージャーを務めるE.S. Jung氏 (提供:日本サムスン) |

SamsungはAppleのiPhone用アプリケーションプロセッサ(A10およびA11チップ)の製造受託を2年続けてTSMCに奪われてしまったことなどもあり、ファウンドリ業界で過半のシェアを握るTSMCのみならず、米GLOBALFOUNDRIESやUMCにも売上高で追い付いていない。そうしたこともあり、Samsungは、ファウンドリビジネスの強化に着手することで、将来、TSMCに追い付くことを目標に非メモリビジネスの中核に育てたいようだ。

14nmと10nmの間に11nmプロセスを導入へ

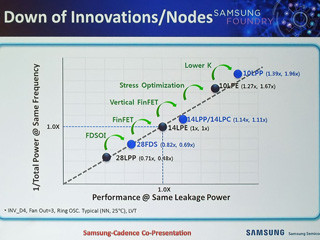

Samsnugは、スマートフォンなどのモバイル向け14nm Fin FET低消費電力プロセスLPP(Low Power Plus)のシュリンク版として、11nmプロセスを採用した11LPPを9月11日に発表し、2018年上半期から量産する計画を発表している。11LPPは14LPPに比べて、同じ消費電力ならば15%性能が向上しチップ面積が10%縮小するとしており、ミッドレンジからハイエンドのメインストリーム機種向けSoCに提供したいとしている。

一方で同社は、すでにハイエンドモバイル向けに10nm FinFETプロセス「10LPE(Low Power Early)」の量産を2016年10月より始めているほか、10nmプロセスの第2弾である10LPP(Low Power Plus)もすでに評価を終えており、近く生産開始をする計画だという。14LPP、11LPP、10LPPとラインアップを拡充するのは、スマートフォンを中心としたハイエンドからミドルレンジに至る多くのモバイルベンダーの要求にきめ細かく応えるためとしている。

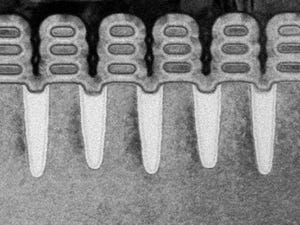

ちなみに同社は、14nm~11nmプロセスをFinFETプロセスの第1世代と位置付け、10nm以降を第2世代と位置付けている。その第2世代としては、10LPPの後に、シュリンク版となる8nm FinFETプロセスが控えており、早ければ2017年末までに生産を始めるとしている。

7nmからはEUVリソグラフィでの量産を計画

さらにその後の計画としては、7nm FinFETプロセスからEUVリソグラフィを適用し、2018年下期にも7LPPの生産を始めたいとしている。同社は、ASMLの「Customer Co-incestment program」に参画し、EUVリソグラフィ量産機開発のための多額の研究資金をASMLに提供しており、TSMCやIntel同様に優先的に新鋭露光装置を入手できる立場にある。量産には250W以上の高出力光源を備えた最新機種を使うとしている。

TSMCは7nm FinFETプロセスの第1弾「N7」プロセスには、従来からの液浸ArFリソグラフィを使い、第2弾となる「N7+」からEUVを使い始めることにしているが、Samsungは最初からEUVに賭けるという。同社はEUVリソグラフィを用いると、液浸ArFのマルチパターニングに比べて、マスク数やプロセス数を削減でき、製造コストを削減できるからと説明しているほか、EUVリソグラフィの試作機を長年にわたって評価してきたことで経験を積んできたので、問題なく量産適用もできる見通しだという。

4nmからは独自のGAA構造を採用へ

7nm以降は、6nm FinFETプロセス「6LPP」や5nm FinFETプロセス「5LPP」の生産を2019年に始める計画とするほか、4nmプロセス「4LPP」も2020年に生産を開始する計画としているが、この4nmからはFinFETに替えて同社独自のGAA FET(Gate All Around FET:ソースドレイン間のチャンネルをゲートで360°取り巻いた構造)である「MBCFET(Multi Bridge Channel FET)」を採用する計画としており、EUVリソグラフィに続いてGAAの採用でも業界一番乗りを目指す。4nm以降は、ショートチャンネル効果でFinFETの電気的特性が著しく劣化してしまうため、GAA構造にせざるを得ないが、これはimecとも共通した認識であるほか、IBMでも5nmからトランジスタ構造をGAAに替えるとしており、今後のトレンドとなる模様だ。

車載やIoT向けにFD-SOIも品ぞろえ

このほか同社は、FinFETプロセスとは別に、主にIoTや車載向けにFD-SOI(Fully Depleted - Silicon on Insulator)プロセスの提供も進めている。FD-SOIはマスクレイヤを抑えた低コスト製造や、低消費電力を特徴としたもので、28nmのFD-SOIプロセス「28FDS」はすでに量産提供をしており、次世代の18nm FD-SOIプロセス「18FDS」も2019年より生産を開始する計画としている。さらに同社は、200mmウェハ1枚に複数の顧客の種類の異なる半導体回路パターンを搭載して多品種少量生産する「MPW(マルチプロジェクトウェハ)シャトル」サービスも開始しており、FD-SOIも含めて品ぞろえを豊富にすることに加え、きめ細かい顧客対応を進めていくことで、ファウンドリ事業の売り上げを伸ばそうとしているようである。

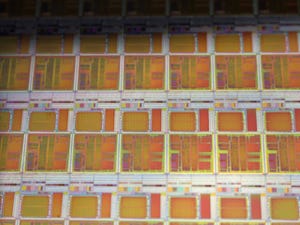

なお、同社のファウンドリ事業部/システムLSI事業部は、韓国器興(キフン)にS1ファブ、米国テキサス州にオースチンにS2ファブ、韓国華城(ファソン)に新鋭のS3ライン(図2)を有しており、特にS3ファブについては、10nmプロセスの増産体制を2017年末にかけて整えるとしている。