横浜にて開催されたIEEE主催のプロセサ関係の国際会議「COOL Chips 20」において、富士通は第12世代目となるプロセサ「SPARC64 XII」を発表した。ポスト京のスーパーコンピュータ(スパコン)では、プロセサはARM v8アーキテクチャに変更することが発表されているが、ビジネスサーバではSPARCアーキテクチャを引き続き使っていくことを明らかにした形である。

このところ、SPARC64やポスト京プロセサの学会発表について富士通では、吉田利雄氏や清水俊幸氏が行うことが多かったが、今回は、丸山拓巳氏の久々の登場である。

SPARC64 XIIプロセサの発表で目を引くのは、12コアという点である。番号順でいうと直前となるSPARC64 XIfxは32個のプロセサコアと2個のアシスタントコアを搭載する34コアプロセサチップであったが、今回のSPARC64 XIIでは、ほぼ1/3の12コアに減ってしまっている。なお、ビジネス系プロセサとしては直前の世代であるSPARC64 X+は16コアであり、それと比べてもSPARC64 XIIはコア数が減っている。

しかし、次の設計思想のスライドに見られるように、SPARC64 XIIは高シングルスレッド性能と高スループットを追求したプロセサである。クロックは4.25GHz(高速モードでは4.35GHz)と4GHzを超える高速クロックで、コア数は減ったものの各コアが8スレッドを並列実行することでチップあたり417G命令/sのスループットを実現している。このスループットはSPARC64 X+の2倍近い。

少ないコア数で高いスループットを実現する仕組みは、まず、各コアがSMTで8スレッドを並列実行するアーキテクチャになったことである。そして、32MiBという大きなL3キャッシュも性能向上に効いている。

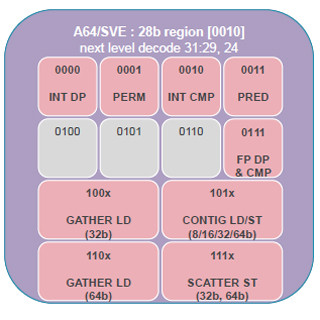

次の図のコア仕様の表をみて気が付くのは、整数と浮動小数点のレジスタファイルと演算器、そして1次データキャッシュが×2pipeと書かれている点である。つまり、1次命令キャッシュと命令のフェッチ系は1つであるが、実行資源は2倍になっており、SPARC64 XIIのコアは、SPARC64 X+のコアのほぼ2倍の大きさになっていると考えられる。そう考えると、SPARC64 XIIでは、16コアのX+から、X+相当では24コアに増えており、スループットが上がっていることに不思議はない。

SPARC64 X+からのマイクロアーキテクチャの拡張点は、実行パイプラインの数を倍増し、8スレッドのSMTとなった点である。実行資源が2倍で、スレッド数は4倍であるので、実行資源の使用がヘビーなアプリケーションでは資源制約となり4倍のスレッドがフルに動かないケースもあると思われるが、資源の利用が少ない使い方の場合はスレッド数に比例した性能が得られる場合もあるので、スレッド数4倍、実行資源量2倍という拡張が有利ということであろう。

そして、分岐予測のやり方の改善や各種のキューのサイズも増大させている。また、クロックを4GHz超に引き上げるためにパイプラインを刻んで、段数を増加させている。

コア以外の部分の変更では、キャッシュレベルを3階層とし、ラストレベルキャッシュとコアユニットをまとめたLCUを4個置くという構成となった。富士通は、ながらくL2キャッシュにこだわってきたが、SPARC64 XIIではL3キャッシュを置くことになり、標準的なキャッシュ階層となった。