|

|

|

図1 東芝 代表執行役副社長でストレージ&デバイスソリューション社 社長の成毛康雄氏 (提供:SEMI) |

2016年12月14日に東京ビッグサイトにて開幕された「SEMICON Japan 2016」併催のスーパーシアター「半導体エグゼクティブフォーラム」において、東芝 代表執行役副社長 ストレージ&デバイスソリューション社 社長の成毛康雄氏が登壇し、「東芝四日市工場でのビッグデータの活用とストレージ事業戦略」と題した3次元NANDフラッシュメモリの事業・製造戦略を語った。

NAND市場は年率40%超の成長分野

成毛氏は、まず、半導体ストレージについて取り巻く環境として、「本格的なIoTやIoEの進展に伴い、世界的にデータセンター需要が拡大する。この結果、世界のストレージ市場は年率22%(2015-2020年の年平均成長率)で拡大していく。特に、NAND型フラッシュメモリとそれを用いたSSD市場が爆発的に拡大するだろう。NAND価格が下落するのに伴い、HDDからSSDへの移行が間違いなく加速していく」と述べたほか、NAND市場について、「NAND市場に限れば、年率40%以上(2015-2020年の年平均成長率)で拡大する。データセンター向けの需要が旺盛なSSDが市場拡大をけん引し、スマートフォンも1台あたりのNAND搭載容量増により需要が堅調に推移するからだ」と、ストレージ市場全体よりも高い成長率を維持するとした。

3D NANDは大容量かつ高信頼性で市場拡大

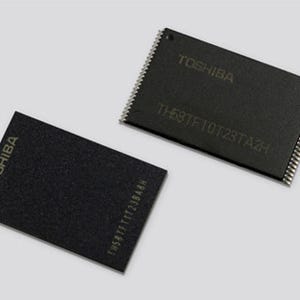

続いて同氏は、東芝が現在量産している3次元(3D)NAND「BiCS FLASH」の第2世代製品(48層のTLC構成)を、15nm世代の2次元(2D) NANDと比較する形で紹介し「BiCSは既存の2D NANDに比べて、記憶素子密度を2倍以上に、信頼性(書き換え回数)を約10倍に、性能(プログラム速度)を約2倍に、消費電力を約半分に、それぞれ改善できる。メモリチップ単体の最大容量でも、15nm世代の2D NANDが128Gビットに留まるのに対し、48層の3D NANDは256Gビットを実現している。第3世代に相当する64層でもすでに256Gビット品をサンプル出荷し、512Gビット品を開発中である」と述べ、このような3D NANDの特徴を生かし、データセンター用SSDをはじめ、大容量、高信頼性が要求される用途を開拓し、市場拡大に努めていくという方針を示した。

200層積層も視野に開発

さらに、「64層3D NAND量産ウェハのライン投入をすでに四日市工場で始めており、量産立ち上げが順調にいけば、2017年は64層品でかなりの供給ビットをカバーできる」と述べた。同社は、今後さらなる高集積化・低コスト化のためにさまざまな技術を開発していくとし、「3次元方向へのメモリセル積層に関しては、100層のセル積層は当然進めるが、200層程度のメモリセル積層にもチャレンジしていく必要があるだろう」と述べた。また、積層数の増加に伴い、縦方向の縮小(薄型化)にも取り組むほか、チップ面積の縮小技術として、周辺回路をメモリセルの下に配置するなど、周辺回路とメモリアレイの効率配置も推進していくことも語った。

肝となる積層プロセスは新第2製造棟で実施

製造に関しては、ナノインプリント(NIL)技術を採用することで、微細化のコスト削減を図り、肝となる成膜・エッチング加工工程に高能率生産性技術を導入するとした。図3に示した東芝四日市工場の製造棟群のうち、この肝になるプロセス工程を担当するのが、2016年7月に竣工したN-Y2(四日市新第2製造棟)である。

BiCS FLASH製造工程は、図4に示すように、大きく「トランジスタ工程」、「メモリセル積層工程」、「コンタクト・配線工程」に分かれるが、この内、積層工程をN-Y2に導入された先端成膜・エッチング装置で処理し、隣接した既存棟(Y3、Y4)と空中搬送通路を通した棟間搬送でやり取りしている。