筑波大学で開催された第8回「学際計算科学による新たな知の発見・統合・創出」シンポジウムにおいて、同大 計算科学研究センターの朴泰祐教授が、筑波大が進めている次期PACSスーパーコンピュータ(スパコン)の開発について発表を行った。

|

|

|

筑波大のPre-PACS-Xについて発表する朴教授 |

筑波大は、東京大学(東大)と共同で25PFlopsのOakforest PACSスパコンを設置しているが、このスパコンは共同利用スパコンで、筑波、東大、京大の3大学で共通仕様を作って調達したT2Kスパコンの後継という位置づけである。

筑波大はもう一系列のスパコンを持っている。それは、1978年から開発してきている「PACS(Parallel Architecture for Computer Science)シリーズ」のスパコンである。PACSスパコンは、1996年のCP-PACSで、Top500の1位になったという歴史を持っている。

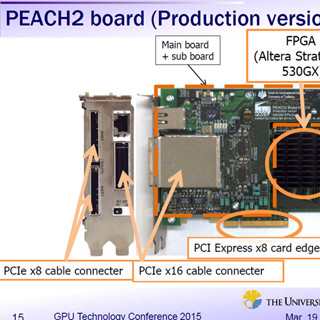

PACSも学内外の研究者に提供されている共同利用のスパコンであるが、並列アーキテクチャの研究という目的もあり、実験的な試みを取り入れている。現在、運用されている第8世代の「HA-PACS」は独自開発の「PEACH2」を使い、GPU間の直接データ転送が行えるスパコンとなっている。そして、第9世代の「COMA(Cluster Oriented Many Core)」はIntelのKNCメニーコアチップを搭載している。COMAは、Oakforest PACSの先行研究と、 Oakforest PACSができる前にメニーコアスパコン向けのソフトを開発するという使い方を意図している。

そして、第10世代目となるのが「PACS-X」であり、Xはエックスではなく、ローマ数字の10である。このPACS-Xを作る前の実験機を作っており、それが「Pre-PACS-X(PPX)」である。

COMAでIntelのKNCも使ってみたところ、SIMDでピーク演算性能を高めているのであるが、個々のプロセサは比較的非力であり、実効性能を上げるにはかなりの工夫が必要であるという。

一方、GPUはNVIDIAを中心に高性能化が続いており、やはりGPUがアクセラレータの本命と考えている。

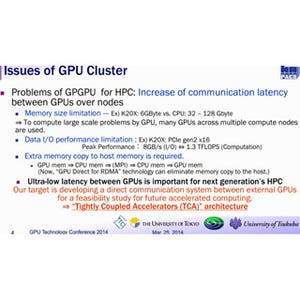

しかし、GPUは柔軟性に欠け、CPUは性能が低い。従って、GPUの高速性とCPUの柔軟性のブリッジが必要である。また、Strong Scalingさせるには低レーテンシの通信が必要である。

そして、アプリケーションやアルゴリズムによって必要な計算精度が変わるが、それらに対応するマルチ精度をサポートしたい。「TCA(Tightly Coupled Accelerator)」の経験から、このような要件を満たすには、FPGAを使うのが有効であると考えている。

そして、アクセラレータをネットワークのスイッチの中に持つというAccelerator in Switchアーキテクチャを作ろうとしている。

Accelerator in Switchは、CPUにGPU群と一緒にFPGAを接続し、FPGAではPEACH2と同様に高速にノード間の直接通信を行う機能と細粒度の部分的なオフロード機能を実現する。

そして、アプリケーションのオフロードについても研究しており、その1つとして宇宙物理部門と慶應義塾大学とLocally Essential Tree(LET)を作成するコードのGPU実装について研究を行っている。現在のコードは、これまでに発表されたコードよりも高速であるが、まだ、高速化の余地が残っている。

また、並列版は計算時間の比で各GPUに割り当てる粒子数を設定しているが、現在の計算時間はMPI通信時間を含んでおり、調整が必要な状態であるという。

LET作成についてはPEACH2を使ってオフロードすることにより、CPUでの実行に比べて2.2倍に高速化され、GPUへの送信までを含めると7.2倍という結果が得られている。

このように良い感触が得られたので、10世代目のPACS-XではGPU+FPGA+短レーテンシネットワークの実現を目指す。それにJST-CRESTで研究中のFPGAへの部分的オフロードを組み合わせる。PEACH2はPCI Expressを使ったためにアドレス空間やデバイス数などで制約があり、PACS-Xでは、この点は改善したいという。

PACS-Xでは、TCAの概念を発展させて、演算と通信の融合を加速させる。通信路は、PCIeより高速で、汎用性、拡張性のある通信系を採用する。

2016年度から調査研究を行い、2018年度をめどに10PFlops程度のPACS-Xを作る計画で、調査研究費で実験システムのPre-PACS-X(PPX)を開発している。PPXは2017年3月から稼働開始の予定である。

PPXの計算ノードは、Xeon E5-2660 v4デュアルソケットにNVIDIAのP100 GPUを2台とAlteraのArria10 FPGAを搭載したBittWareのボードを接続する。このボードは40GbEを2ポート持っている。また、MellanoxのEDR IB NICも装備する。

そして、PPXでは、この計算ノードを6ノード使いIB/EDRスイッチと40GbEのスイッチで接続する。

PPXの技術的課題であるが、ノード内のCPU、GPU、FPGAを結合しているのは、依然としてPCIeで、FPGA接続がGen3×8レーンで一番貧弱である。FPGA同士は40GbEで高速通信、GPU同士はIB/EDRで高速通信ができるが、この2つをどう連携させるかも問題である。

GPUはOpenACCやCUDAでプログラムできるが、FPGAをどうプログラムするのかは課題である。OpenCLでプログラムできるが、まだ、性能、記述性ともに不十分であるという。

ノード内の接続は、PCIeを使い続ける、IntelのFPGA内蔵Xeonを使う、OpenPOWERを使いNVLINK2で接続、OpenCAPIを使うなどが考えられるが、色々と問題がある。

FPGA間については、100Gbpsの光リンクを使うという手もあり、接続実験を行っている。接続トポロジは、次の図の(A)、(B)、(C)を実験している。(A)では理論ピークの96%の性能が得られ3チャネルを動かしても良いスケーラビリティが得られる、(B)でもバンド幅の低下は僅かで、FPGAの通過レーテンシは20ns程度であるという。

まとめであるが、第10世代のPACSに向けての研究を開始した。GPUとアクセラレータを接続するマルチヘテロ環境を想定したアクセラレータシステムの骨格を作る。そのために、まず、Pre-PACS-Xを作って、各種の実験を行う。そして、2018年度をめどにPACS-Xを作ると朴先生は、結んだ。