Hot Chips 28において、AMDは次世代コア「Zen」を発表した。発表者は、シニアフェローのMike Clark氏である。

|

|

|

Hot Chips 28でZenを発表するAMDのMike Clark氏 |

Zenの最大の売りは、現在のExcavatorコアと比較して40%も高いIPCである。つまり、同じクロックで40%高い性能を発揮するプロセサコアであるということである。

そして、40%高い性能を、Excavatorコアと同じ電力で実現するという。

それをどのように実現したかを示すのが、次の図である。この図にはコアエンジンの改良項目が11項目、キャッシュシステムの改良項目が7項目、低電力化の改良項目が7項目の銅系25項目が並んでいる。

2スレッド/コア化、つまり2スレッドのSMT化はIPC向上にはかなり効果があり、IPC 40%向上の半分くらいは、このSMT化効果ではないかと思われる。それ以外では、分岐予測の改良やL1キャッシュのライトバック化などの貢献が大きそうである。仮にSMT化で20%の向上とみると、残りの24項目で20%の改善であるので、20%/24=0.83%であり、項目当たりの改善は0.83%である。つまり、多数の小さな改善を積みかさねて、40%の改善が実現されている。

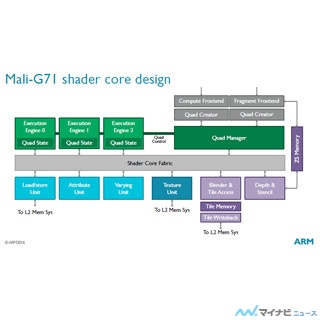

次の図にZenコアの全体像を示す。

これまでのAMDのコアは単一スレッドを実行するコアであったが、ZenのコアはIntelのCoreプロセサと同様に2スレッドを並列に実行するアーキテクチャに変った。これはIPCの向上には大きく貢献していると思われる。ただし、この改善はマルチスレッドが生きるアプリケーションでなければ役に立たない。

Zenコアは、4つのx86命令をフェッチする。分岐予測に基づき、命令キャッシュから命令をフェッチしてデコードし、Micro-opキューに格納する。そして、命令の実行は整数系と浮動小数系に分かれており、整数系は6個のスケジューラに4個のALUと2個のAGU(Address Generation Unit)が繋がっている。整数レジスタファイルは共用である。整数レジスタファイルは168エントリを持つ。単一スレッドを実行する場合は、全エントリを1つのスレッドで占有できるので、192命令がIn-Flightになることができるという深いOut-of-Order実行ができるように設計されている。一方、2スレッドで分割して使用する場合は、スレッドごとには84エントリとなり、従来のプロセサより少ないレジスタ数となる。

浮動小数系は単一のスケジューラで、2個の乗算器(MUL)と2個の加算器(ADD)を動かしている。これで128FMACを実行する。

ロードストアユニットは2個で、72個のOut-of-Orderのロードをサポートする。2つのAGUが生成したアドレスはLoad/Storeキューに送られ、1次データキャッシュをアクセスする。

1次命令キャッシュは64KB、4way、1次データキャッシュは32KB、8wayである。そして、2次キャッシュは512KB、8wayで、Zenコアには含まれないが、チップ全体としては大容量(8MB)の3次キャッシュが付く。

Zenコアの分岐予測は、ハッシュ・パーセプトロンを使っている。TLBを通してVAに変換してからキャッシュを読む方式で、L0 TLBは8エントリ、L1TLBは64エントリ、L2 TLBは512エントリと3階層のTLBを備えている。BTB(Branch Target Buffer)もL1とL2の2階層で、各エントリは2つの分岐を記憶する。リターンスタックは32エントリで、さらに、間接分岐を扱うITA(Indirect Target Array)を持つ。

命令キャッシュは64KBで4wayとなっており、マイクロOPをキャッシュするためにマイクロTagを持っている。

バイト単位の命令バッファから、命令の切れ目を見つけて、4つのx86命令を切り出してデコードする。また、Opキャッシュから読み出したマイクロ命令とあわせて、マイクロOpキューに入れ、命令によってはマイクロコードROMを読み出したり、Stack Engine Memfileを読み出して命令を取り出してディスパッチに送る。デコーダは、整数演算部には最大6マイクロOp、FP部には最大4マイクロOpを送る。

整数演算部には4つのALUの命令キューと2つのAGUの命令キューがあり、各キューは14エントリとなっている。レジスタファイルは168エントリと大きいのであるが、SMTの2スレッドでシェアされていると考えられるので、スレッドあたりで見るとそれほど大きくはない。