こちらのレポートの最後でも触れた通り、10月2日にPCI-SIGはDevelopers Conference Asia-Pacific Tour 2015を東京都内で開催した。ちなみにスケジュールは

- 9:00am - 10:30 am PCI Express Basics & Background

- 11:00am - 12:30 pm PCIe Electrical Basics

- 1:30 pm - 2:30 pm PCIe 4.0 Encoding Update

- 2:30 pm - 3:30 pm PCIe 4.0 Protocol Update

- 3:30 pm - 4:00 pm PM Break and Exhibit

- 4:00 pm - 5:00 pm PCIe Form-factor Updates

- 5:00 pm - 6:00 pm PCIe 4.0 CEM & Electrical Previews

といった感じで、ほとんどがPCIe 4.0に関する話で埋まっている状況である。ちなみに参加者はPre-registeredが125名ほどで、このうち100名ほどが参加したとか。当日朝は東海道線にアルミテーブルが投げ込まれたり、山手線で人身事故があったりで大幅にダイヤが乱れており、それを考えればむしろ参加率は高かったというべきか。

このAsia-Pacific Tourに参加できるのはPCI-SIGの会員企業のみであり、プレスカンファレンスなども開催はされなかったのだが、幸いにもRichard Solomon氏とReen Presnell氏に話を伺うことができたので、その内容をまとめてご紹介したいと思う。

まず、久しぶりに日本で開催を行った理由について「われわれは通常、18カ月~24カ月ごとに各地をまわることにしているが、ここしばらくは(APAC地域では)台湾における(PCIe 3.0の)Compliance Programにリソースを集中していた。ただこれはやっと一段落した」という。さすがにPCIe 3.0に関してはもうテストスペックも完全にリリースされ、互換性の問題も殆ど見られなくなってきたので、そろそろPCIe 4.0について話をする頃合いであろうと判断したものと思われる。

PCIe 4.0は順調に進捗

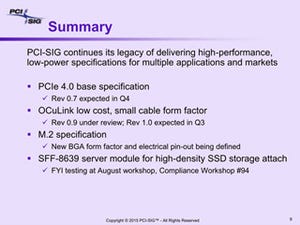

さて、そのPCIe 4.0について。以前の進捗を振り返ると、現時点ではまだBase Spec Rev 0.5の状況だが、2015年第3四半期中にRev 0.7となり、2016年後半にはRev 0.9になるとしている。スケジュールについて確認すると「現時点では非常に順調だ。作業はElectrical WorkgroupとProtocol Workgroupそれぞれで行っているが、どちらもRev 0.7に向けて解決すべき問題のリストは非常に短い」とした。

実際のところ、Protocolに関して言えばRetimerが事実上標準になったことと、LTSSM(Link Training Status State Machine)周りが変更になったこと程度で、後はGen3と違いが無いという。

Retimerは以前こちらで紹介したが、信号路が長すぎる場合に、波形が乱れてしまうことを防ぐため、一定間隔でRepeaterを挟み込む必要があり、これに関する規定である。Solomon氏いわく「Gen3ではほとんど使われなかったからこれをインプリメントするベンダーはあまり無かったけど、Gen4ではこれが必須になる」とのことだ。

一方LTSSMは要するに通信を開始する前に、通信路の状況などを確認して相手とどの程度の速度で通信できるかを確認するための初期化シーケンスだが、今回は16GbpsのGen4が加わる以上、当然ここにはGen4の速度確認のプロトコルが追加されるわけで、変更は必須である。

ちなみにその初期ネゴシエーションであるが、これまでだとGen1→Gen2→Gen3という形で速度を上げていったのに対し、Gen4ではGen1→Gen3→Gen4となるそうだ。で、Gen2に関してはGen1 OK→Gen3 NGとなった時点でGen2に速度を落とす形になるらしい。

ちなみにGen 3ではRev 0.7からRev 0.9に進む間にRev 0.71が挟まり、これで半年以上の遅れが出たほか、スペックそのものが変更になった関係で、Rev 0.7をベースに開発を行っていたベンダーにもかなりの影響を及ぼすこととなった。

これと同じことがGen4でも発生しないか? と確認したところ「そうならないように最大限の努力を払っている。われわれはRev 0.7の策定にあたり、すべてのポイントに注意を払い、メンバー企業に(0.71の時に生じたような)追加作業を行わせないで済むようにしなければならないからだ」ということで、Gen 3のRev 0.71はかなりPCI-SIGにとってトラウマだったことをうかがわせるものだった。

PCIe 4.0のターゲット

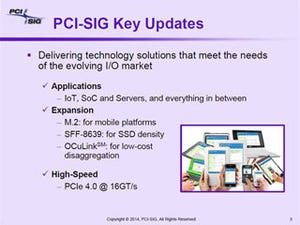

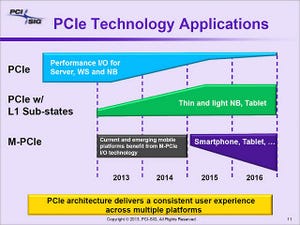

ところでそのGen4、ターゲットアプリケーションを見ると、Gen3ではGPUが落ちつつも、まだGPGPUに代表されるアクセラレータは対応範囲としていたが、Gen4ではこれらも落ちてしまい、もうStorageのみという感じになってきてしまった。ついでに言えば、PCIe Switchを使ってのシステム構築に関してもすっかり姿を消した感がある。

このあたりを確認したところ「確かにUltra Highendの構成では、すでにGen4は適さない。そこにGen5(笑)が来るかどうかはよく分からないが。ちょっと昔に戻ると、Gen2のころにStorage業界の人間は"SASは6GなのにPCIeは5Gしかない。もっと速く!"とか言っていたわけで、常に追いかけっこになる。真面目に答えると、2016年末には16Gの仕様策定がほぼ終わるが、多分その時にも"それでは足りない"という人は居るだろう。ただ、重要なのはこれが標準I/Fだということだ。もちろんProprietaryなI/Fならもっと高速なものが手に入るだろうけどね」とした

さらにそのうえで「確かにUltra HighendのGPGPUにはGen4では足りないだろう。ただ、そうしたハイエンドを除くと、PCIe Gen4でも十分な性能を提供できると思う。加えるなら、ストレージマーケットにはPCIe Gen4が広く使われると思う」とした。

最近だとStorageコントローラから直接ネットワークが出る形態も増えつつあるが、「最終的にはエンドユーザーの選択だが、Ethernetに比べるとPCIeの方がオーバーヘッドが少ないから、共存してゆけると思う」との話だった。

もう1つがSwitchである。MR-IOV Switchを利用してサーバーを構築するというアイディアは、2008年~2010年ごろに盛り上がったのだが、最近はEthernetを使ったシステムの方が一般的であり、特にOpenStackとかNFVが急速に盛り上がった昨今では全く見なくなりつつある(もちろんNFVは仮想化が大前提なのでSR-IOVは当然の様に利用されている訳だが)。

これについて尋ねたところ「メンバー企業の中で1社、StorageベースのSwitchをリリースしてはいる」とした上で「公開した仕様の全てが必ずしも広く使われる、とは限らないし、われわれはそこまで影響を及ぼせるわけではない」と、割と諦め顔ではあった。

PCIe 4.0のその先

ちなみにGen4の次は? と水を向けたところ「まだその議論をするには早すぎる」とし、「その昔、Gen2の時に似たような議論をしたことがある。その時には、そもそも5GT/secが実現できるかどうか分からないなんて話すら出ていた。ところがいまは16GT/secの話をしているわけで、どこまで性能が上がるかは予測がつかない。要求もそうだ。例えば今は100G Ethernetがある。ただこの先もっと高速なEthernetが出てきたら、さらに高い帯域が要求されることになる。どこまで上がるか、誰にもわからない」とした上で「個人的な見解としては、後方互換性が維持されるのはGen4までで、もしその先があったとしてもそこでは(Gen4までとの)互換性は維持されないだろう。また銅配線か、光かはコストとのトレードオフになると思う。今の光は決して安価ではない。もし光接続のコンポーネントが十分安価になれば、光接続の可能性はあるだろう」という見通しであった。

ちなみにここでいう互換性はあくまでも電気あるいは機械的な部分の話で、プロトコルそのものは(PCI→PCIeの時と同じように)互換性を保つのではないか? という話だった。

さらにPCI-SIGとしてのGen4のターゲットプロセスは? と確認したところ「ボリューム生産が行われるプロセスということになるので、現在の状況を見る限り14/16nmのFinFETプロセスが主なターゲットになるのではないかと思うが、最終的には業界の動向次第だ」とした。

さて、インタビューそのものはもう少しあったのだが、余談に近いのでこちらは割愛して、もう少しPCIe Gen4の話を。先にプロトコルは基本的には変わらないという話をしたが、では電気的には? というとこれも意外にGen3の延長というか、基本的にはあまり変わらないままでいけるらしい。ただし、リファレンスデザインでは受信側のイコライザーが若干強化されることになる模様だ。

では、電気的にまったく変化がないといえるか? というとそんなこともなく、到達距離がラフに言って半分になるそうだ。具体的に言えば、PCIe Gen3のCEMでは"Client CEM"と呼ばれていた、要するにPCのマザーボード向けのフォームファクタだが、配線長が最大12inchでコネクタが1つ付くものはGen4でもサポートされる(というか、したい)としている。

ところが"Server CEM"、つまりサーバーのバックプレーン向けとなる20inchの配線長+2コネクタのフォームファクタは放棄された。8GT/secでもぎりぎりだった(からこそRetimerがECNの形で追加された)ので、16GT/secとなるともはや信号の劣化が激しすぎるらしい。

ではサーバー向けはどうするかというと、10inch程度ごとにRepeaterを挟む形で解決することになる。Gen3の世代でも20inchを超える配線長のバックプレーンでは、間にRepeaterを挟む必要があったが、これが半分になる計算だ。もちろんこれはFR4をベースにした話で、もっと品質の良い配線材料や絶縁材料を使えばこの限りではないのだが、方向性としては配線長がシビアに影響する事になる見通しになりそうだとのことである。

ちなみにPCIe Gen4に対応するPIPE I/FはVersion 4.2になるそうだ。PCIeだけで言えばVersion 4.0で対応できるはずだったが、USBなどもPIPE I/Fを利用する関係で4.2になったのだそうだ。

展示の様子も紹介

ということでPCI-SIGからの話はこんな感じだが、メンバー各社は? ということで展示の内容も簡単にご紹介。基本的に各社それなりにPCIe Gen4に向けて走り始めている。Synopsysは今回Gen4対応PHYのデモを行った(Photo03)ほか、CadenceはDIP(Device IP)のみならずVIP(Verification IP)のGen4対応をアピールしていた。ちなみにSynopsysのIPはRev 0.5相当、CadenceのVIPはRev 0.3相当だが、これは今後のBase Specificationにあわせてバージョンアップするという。

|

|

Photo03:Photo03:一番上はARCコアベースのLinuxが動いているプロセッサ、その下にあるのはPCIeのトランスポートレイヤを実装したVirtex-7が載った汎用ボードで、一番下にあるのが28nmで試作したGen4対応PHYとのこと |

PLDAもGen4に対応したIPを提供する用意があることを明らかにしていた。実は今回初めて聞いたのだが、PLDAはUSB関係のIPの提供はUSB 3.0で打ち止めにしており、今はPCIe IPをメインにしているとのことだ。理由はというと、USBはどんどん仕様が複雑になってきており、対応しきれなくなったからとしている。

Mentor GraphicsもやはりPCIe 4.0対応のVerification IPを用意している。また測定器関係ではKeysightとTektronixがGen4に対応したソリューションを準備中である。どちらも測定器そのものは既存のストレージオシロで速度的には十分対応可能で、プロトコルも既存のGen3対応のものが「大部分は」利用できるが、なにしろBase SpecがまだRevision 0.5の段階なので現時点ではまだ正式対応という訳にもいかないのだろう。

そんなわけで正式対応はソフトウェアの作業のみということで、Base Specificationにやや(平均1四半期)遅れて策定されるTest Specificationにあわせる形できちんとリリースしたい、という話だった。この分野ではLeCroy(現Teledyne LeCroy)がGen1のころから早いタイミングで対応製品を出していた事もあって、結構大きなシェアを伝統的に獲得している。ただ同社の測定器は価格が高めなことでも有名であり、そんなこともあってか両社ともにGen4には早いタイミングで製品を投入できれば価格競争力があると見込んでいるようだ。

ちょっと異色だったのがVIAVI SolutionsとSerialTekである。VIAVI SolutionsはJDSU(JDS Uniphase Corporation)という会社のネットワーク部門だった。同社は2015年にLumentum Holdings IncとVIAVI Solutionの2社に分離しており、前者は通信機器向けの光コンポーネントやサブシステムを、後者はネットワークシステムそのものを扱っている。

VIAVIの方はさまざまな測定機器も扱っており、すでにXgig 1000 PCIe Gen3 Analyzerなどをリリースしているのだが、今回はこれに新しくPCIe Gen-3 Jammerが追加された事を展示していた。ハードウェアはAnalyzerもJammerも一緒で、内部のFPGAにロードするファームウェアが違うだけだとか。

Gen4対応については、PCIeのBase Spec、それとIntelの製品のGen4対応に合わせる(通常Intelの方がやや先行する)予定だが、「さてIntelのGen4対応はいつだと思う?」とお互いに聞きあって笑うという状況だったので、もう少し対応製品が出るのは先かもしれない。

一方のSerialTekは、PCIeのみならずM.2あるいはU.2、NVM Expressなどのテスト用のInterposerとAnalyzerを提供するベンダーである。特にM.2の場合、StorageとPCI Expressの両方の用途があり、あるいは最近はU.2なども登場してきたことで、これらの開発やテストに向けたインターポーザーを用意して迅速に開発ができる事を強調していた。さすがに同社の場合、PCIe Gen4はまだ先の話だとしつつ、ただしBase SpecificationがRev 1.0になるタイミングではちゃんと対応するとのことだった。

ということで簡単にPCI-SIG Developers Conference Asia-Pacific Tour 2015 Reportの内容をお届けした。現時点ではまだGen4は審議中ということで、非会員に対しては基本情報公開を行っていないので、あまり突っ込んだ内容をご紹介できない事はご容赦いただきたい。いまのところPCI-SIGサイドは「一応」順調に進んではいるようだ。

問題はこれをインプリメントする方であろう。Base Specificationは順調に行けば2016年末までにRev 0.9に達する。通常0.9→1.0は仕様書の文言とか抜けの修正などで、仕様そのものが変わることはないから、大体どのメーカーもこの時期になったらインプリメントを開始する。

逆に言えば、IntelだったらKaby Lakeは絶対に間に合わないし、Broadwell-EPも無理で、恐らくSkylake-EPとかCannonLake(なのかIceLakeなのかはっきりしないが)の世代以降にならないと実装されないことになる。

AMDはZenベースの初代製品には間に合わない公算が大きく、その次以降の対応になるだろう。つまり現実問題としては2017年以降の製品にしか搭載されないことになる。ただ、実際にどのタイミングで採用されるか(あるいはそもそも採用されないか)は、もう少し時間がたたないと見通せない状況ではあるが、Gen3の時ほど難航しそうにはない、というのはちょっとうれしいニュースかもしれない。