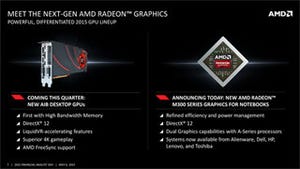

既報の通り、米AMDは6日(現地時間に)に開催したFinancial Analyst Meetingの中で、次世代GPU製品にHBM(High Bandwidth Memory)を採用することを明らかにしているが、このHBMに関するもう少し詳細な情報が同社のJoe Macri氏(Corporate VP, Product CTO and Corporate Fellow)から電話会議の形で説明があったので、その内容を紹介したい。

もともとMacri氏は半導体分野の標準化団体であるJEDECのBoardメンバーで、JC-42.3(Subcommittee: DRAM Memories)の議長も勤めている。そのため、既存のGDDR5の限界もよくわきまえた人である。HBMの策定にはかなり初期から関係しており、その意味では氏が携わってきたHBMがやっと製品の形で登場するということになる。

GDDR5が直面する課題

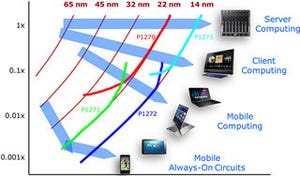

さて、HBMを利用するそもそもの動機であるが、Photo01にあるようにGDDR5メモリは、パフォーマンスと消費電力で課題に直面している。ご存じの通りPC用メインメモリは、FPDRAMからSDRAM/DDR/DDR2/DDR3/DDR4と高速化するついでに電圧を下げることで、何とか全体としての消費電力を一定の枠内に収めてきた。

|

|

Photo01:GPU Performanceが中折れになるのは、メモリ帯域が増えないためである。その先で急降下しているのは、メモリの消費電力がこのまま増えてゆくと、相対的にGPUの消費電力を下げる必要があり、むしろ性能が落ちることになるという話である |

ただそのDDR4でも信号速度は最高でも4.26GHz程度でしかない(というか、現状出荷されてるものは2.13GHz程度にとどまっている)。GDDR5は最大7GHzあたりまで引っ張っているが、こちらもそろそろ頭打ちになってきた。しかもDDR4と比較すると、GDDR5は電圧が高いから消費電力がばかにならない。この先、帯域をさらに必要とするケースでは、あとはバス幅を広げるしかないのだが、そうすると消費電力が増えることになる。

まぁ当初はGDDR5は5GHz程度が上限といっていたのが、いまでは8GHzまで引っ張ることが可能という話になっており、これはこれですごい話ではある。それでも9GHzとか10GHzの展望は全く見えていないから、やはり前述したように現状ではバス幅を増やすしかなく、これは必然的にチップ数が増えることになる。

結果として、GPUの周囲に多数のチップがぶら下る形になり、実装面積が大きくなってしまう(Photo02)。理想をいえばもう少しGDDR5チップをGPUに近づけたいのだろうが、信号の配線を考えるとこれでも近すぎるくらいで、もう少しゆとりを持たせたいところだ。ところが、GDDR5チップとGPUに距離があるとLatencyが増え、波形が鈍り、消費電力が増え……といった形で別の問題が生じてしまう。110mm×90mmという実装面積は、このあたりのせめぎあいの結果といえる。

|

|

Photo02:ちなみに4GB構成なら表面だけの実装だが、8GBの場合は裏面にも同じ形でGDDR5チップが配されることになる。これのおかげで、ビデオカードの基板は10層以上が必要であり、これがまた高コストに繋がる |

こうした問題は、いっそDRAMをオンダイで搭載すれば話は解決する。実際こういう考え方でeDRAMを利用したGPU(になる以前のグラフィックコントローラ)は少なくない。しかし、昨今のGPUで要求される容量のメモリをeDRAMで実装するのはやはり非現実的である(Photo03)。加えていえば、昨今のGPUで要求されるメモリ帯域について考えたとき、オフチップでDRAMを接続することそのものが、難しいという話は当然ある(Photo04)。

これに対する解決案は、Intel/Micronの開発したHMC(Hybrid Memory Cube)、WideIO/WideIO2、それとHBMということになる。このうちHMCは、帯域はともかくGPUチップとDRAMの距離が結構あるので、消費電力が高くなる。WideIOやWideIO2は、帯域と消費電力の観点では理想的であるが、

- WideIOを実装するためのTSV(through silicon via:シリコン貫通ビア)の実装が高コストすぎる

- GPUの消費電力は全然減らない、ということはWideIO構成にするとスタックしたDRAMチップはGPUの熱で激しくあぶられることになり、まともに運用できる気がしない

といった辺りが大きな問題として考えられる。そこでAMDとしては、HBMを使ったソリューションを採用することになったとする(Photo05)。

具体的な実装方法

具体的な実装方法は、Photo06を見てもらった方が分かりやすいかもしれない。一番下にあるのがPackage Substrateで、これはこれまでのGPUと違いが無い。ところがその上に、Interposerと呼ばれるレイヤが入る。これはSiliconをベースに製造される中間層だ。GPUとHBMはこのInterposerの上に実装される形になる。これを真横から見たのがPhoto07である。

このInterposerを最初に採用した商用製品はXilinxのVirtex-7シリーズで、当時同社はこの技術をSSI(Stacked Silicon Interconnect)と呼んだが、同社のSSIの場合、2つのFPGAのダイ間を10,000本以上の信号線で接続している(技術的には35,000本以上が可能、という話だった)。

HBMとのバス幅は1024bitになるが、Interposerを使えばこの程度の本数は難しくもなんともない。ちなみにHBMやGPUとInterposerの間はMicrobumpと呼ばれる微細なBallで接続されるが、このMicrobumpの間隔は100μm程度とされる。

HBMとGDDR5のスペックを比較したのがこちらである(Photo08)。転送速度を低く抑えているため電源電圧は1.3Vと低めだが、バス幅が1024bitなので、1024Gbit/sec=128GB/secの帯域が1つのHBM Stackで実現できる。

ちなみにPhoto09は2014年のHot ChipsにおけるSK Hynixの講演資料からの抜粋だが、こちらだとVDDが1.2Vになっているにも関わらず、Photo07で1.3Vとやや高めになっているのは、1.2V動作を目指して製造したものの、実際には1.3Vを掛けないと安定して動作しないというあたりが正解な気がする。

|

|

Photo09:講演はHC26.11.310の"HBM: Memory Solution for Bandwidth-Hungry Processors"で、同社のJoonyoung Kim氏とYounsu Kim氏によるものである |

SK Hynixは2014年からHBMのサンプル出荷を開始しており、そろそろ量産に入っている。今回利用されるのはPhoto09でいうところの第1世代であるが、それでも既存のGDDR5と比較すると大幅にメリットがある。

HBMの採用によるメリット

1つ目は帯域/消費電力比の改善で、GDDR5が10.66GB/sec/Wに対しHBMは35GB/sec/W以上であるとする(Photo10)。

実装面積の最小化も大きなテーマで、既存のGDDR5は基板に直接搭載するのであまりBall Pitchを縮めることができなかった。そのため、チップ辺り14mm×12mm程度の面積が必要になっていた。一方、HBMはMicrobumpでInterconnectとつながるから、ほぼDRAMのダイサイズそのままに近いパッケージで済むことになり、大幅に実装面積の節約が可能である(Photo11)。この結果として、HBMベースのGPUは70mm×70mmと、ほぼGPUのパッケージ+α程度の面積で実装できるという。

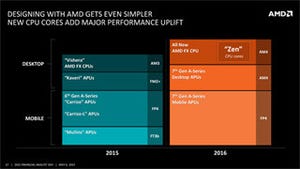

さて、Macri氏の説明内容はこんなところであるが、若干の補足をしておきたい。まずメモリ容量の話。現在はAIB(Add-in-Board)パートナーの意向で、複数のメモリ構成が可能である。

GDDR5の場合、同じメモリ容量のままバス幅をx16とx32で変更可能であり、例えばRadeon R9 290Xの様な512bitバスの場合は

- 32bit幅×16個:メモリ容量4GB

- 16bit幅×32個:メモリ容量8GB

の2つの構成が可能である。8GBの場合は、基板の裏面にもGDDR5チップを実装するわけだ。ところが今回のHBMソリューションの場合、メモリの実装はAMDの作業になっているのだが、Photo11の構成だと4GBの容量しか搭載できないことになる。

これはなぜか。実はSK Hynixは当初、HBMの第1世代でも1GBと2GBの2種類の容量を出すという話をしており、これが実現していればAMDの側で4GB版と8GB版を用意すれば済む話だった。しかし、Photo09にあるように、第1世代は1GBのみしか存在せず、大容量製品は第2世代送りになってしまった。ということで、いまのところ8GB容量の製品がどうなるのかは全く不明である。一部にはHBMチップを8つ搭載という観測もあるようだが、さすがにそれは考えにくいと思う。

もう1つは放熱の話。Photo12を見ると、まるでボード全体の面積も大幅に縮まるように思えるが、実際にこれまでのリファレンスカードを見ると、GPUチップには巨大なヒートシンクが付けられ、これをさらに複雑なファンと組み合わせて一種のウィンドトンネルを構成する様な構造になっている。

|

|

Photo12:余談だが、HBMの方のASICのサイズがR9 290Xのものと殆ど変わらないのは象徴的である。2015年6月に登場すると予想されているFijiに最初に使われることになるのだろうが、そのFijiはR9 290X+HBMといった構成であっても筆者は驚かない |

ボード面積を縮めるためには、このあたりも小さくまとめるための工夫が必要になるわけだが、果たしてそれが可能か? というのはちょっと怪しいところだ。もちろん液冷ユニットを突っ込んでしまえば可能だとは思うが……。最終製品はともかく、リファレンスカードそのものの長さは従来製品とあまり変わらない気がする。

ただし、基板そのものはずっと安価になるだろう。これまではGDDR5への信号線を通す必要があったから、10層以上の多層基板が必要であった。ところがHBMを使うとそうした信号は全てInterposerを流れるので、基板側までつながっているのは電源とGND、それとPCI Expressの信号、あとは出力信号(DVI/DisplayPort/HDMI)のみである。さすがに4層程度では足りないかもしれないが、少なくとも10層とかの多層基板はもう必要がなくなり、これは多少なりともコストダウンにつながるだろう。