2014年11月のGreen500で2位となった高エネルギー加速器研究機構(KEK)の睡蓮スパコンを開発したPEZY ComputingとExaScalerであるが、実は、PEZYグループには、もう1社、Ultra Memoryという会社がある。

2月20日に大阪で開催されたPCクラスタワークショップin大阪2015において、PEZYの齊藤社長が講演し、その中で、第2世代のPEZY-SC2では3D積層の広帯域DRAMを使うという計画を明らかにした。

3D積層の広帯域DRAMに関しては、NVIDIAのPascal GPUではHBM(High Band Width Memory)を使うことを明らかにしており、IntelのKnights LandingはMicronのHMC(Hybrid Memory Cube)を使うと言われている。また、富士通のFX100スパコンではすでにHMCが使われている。

このように、高性能で広いメモリバンド幅を必要とするスパコンなどのプロセサでは、3D積層の広帯域DRAMの採用は常識となってきていて、PEZYの次世代チップであるPEZY-SC2での採用は驚くにはあたらない。しかし、驚くのは、NVIDIA、Intel、富士通などの大企業がDRAMメーカーの標準製品(正確には、IntelのKnights Landingはキャッシュタグなどを含むカスタム品と言われている)を使うのであるが、PEZYはグループ内に持っているUltra Memoryで3D積層DRAMを自社開発し、それを使おうとしているという点である。

つまり、アクセラレータ側はPEZY-SC2も3D積層DRAMも自社開発して性能を追求するというアプローチを取る。標準製品の3D DRAMは、HBMは128GB/s、HMCは10~15Gbps×8レーン×4chで、160~240GB/sの帯域となっている。これに対して、Ultra Memoryの3D積層DRAMは500GB/sと、MicronのShort Reachの15Gbit/sのHMCと比べても2倍あまりの帯域をもつという計画である。

Ultra Memoryを率いるのは安達隆郎氏である。安達氏は、元エルピーダメモリの取締役、CTOを務め、3Dメモリの開発を推進してきたという経歴を持つ。その安達社長に話をうかがったところ、500GB/sという広帯域を実現するにはDRAMチップ間の接続本数が非常に多くなり、TSV(Through Silicon Via)の歩留まりが低くなってしまうのが大きな問題とのことである。そこで目を付けたのが、慶應義塾大学の黒田忠広 教授が開発した磁気結合での信号伝送技術であるという。3D積層したDRAMチップ間の信号伝送は磁気結合で行い、積層DRAMとPEZY-SC2の間の信号伝送も同じ磁気結合を使うという。

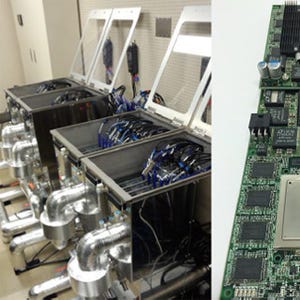

2014年のVLSI Symposiumにおいて、東京工業大学、DISCOとPEZYの共著の「Ultra Thinning Down to 4-μm using 300-mm Wafer Proven by 40-nm Node 2Gb DRAM for 3D Multi-Stack WOW Applications」という論文が発表されている。2GbitのDRAMチップを搭載する300mmウェハを4μmまで薄く研磨し、それをWafer On Waferで積層するという論文である。

安達社長によると、磁気結合は実用的には100μm程度が限界で、100μm厚のチップの場合は2枚、50μm厚でも3枚程度しか積層できない。しかし、4μmまでチップを薄くできると8枚かそれ以上の積層が可能になり、超薄研磨と磁気信号伝送の技術を組み合わせると、大きなメリットが生まれるという。

磁気結合であれば、TSVのように断線という心配はない。電源とグランドは直流を通せるTSVを使う必要があるが、こちらは多数本の並列接続となるので、不良の断線したTSVが多少あっても問題にはならないので、TSV接続の歩留まり問題は発生しないという。

また、DRAMチップ間、積層DRAMとPEZY-SC2の間も同じ磁気結合で、広帯域で接続できるとのことである。