米Xilinxは3月9日(現地時間)、同社が高位合成ツールとして提供しているSDxシリーズに新しく、Embedded System向けとなる「SDSoC」を追加した。当日は米本社よりHugh Durdan氏(Photo01)が来日、SDSoCの詳細を説明した。

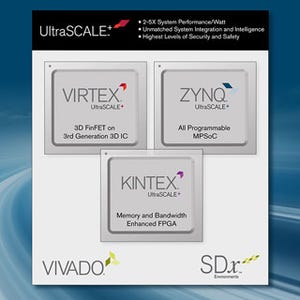

そもそもSDxシリーズは、同社のVivadoの上位ツールにあたる製品である(Photo02)。最初の「SDNet」はPacket Processing向け、次に登場した「SDAccel」は、Data CenterやMedicalなどの用途に向けたもので、いずれもC/C++などからFPGAのLC(Logic Cell)を簡単に利用するためのツールであるが、SDSoCはこれに続く製品ということになる。大きな違いは利用形態である。SDNetでは、SDN(Software Defined Network)に対応した形で、独自のSDNetコードと呼ばれる(C/C++風の)コードを与えると、それに合わせて自動的にFPGAへの実行イメージが生成される。またSDAccelではC/C++/OpenCLの形でアプリケーションを記述しておき、これをFPGA上で実行させる、ある種クロスコンパイラとも言えるものになる。なのでこの2つはFPGA FabricさえあればXilinxのどのFPGAでも原則動作するものであるが、SDSoCはZynqおよび(先日発表された)Zynq MPSoCのみが対象となる(Photo03)。

|

|

|

|

Photo02:ちなみにSDSoCそのものは以前から準備は出来ていたそうで、ただし本社の意向でUltraSCALE+の発表を先行した関係でやや発表が遅れたとか |

Photo03:対象となるのはARMコアを搭載したFPGAということで、以前のPowerPC 440 Virtex-5などはもちろん対象外 |

さて、ではSDSoCは何を目的としたものか、というと端的に言えば「(Zynqの)ARMコア上で動くC/C++アプリケーションの一部をFPGAのLogic Cellを利用して高速化できるツール」である。ZynqのようなCPU+FPGAの構成では、CPU側はソフトウェアですべて記述できるから自由度は高いものの性能は高くない。逆にFPGA Fabric側は性能は猛烈に高いが、RTLとは言わないまでもVerilogなどを使う必要がある。同氏はざっくりと「RTLを記述できるエンジニアの1000倍くらい、C/C++のエンジニアが居る」(つまりC/C++のエンジニアの中で、RTLなりVerilogなりがかけるエンジニアは1000人に1人位の比率)としており、この結果として折角のFPGAの高速性を生かすことが出来ない状況が続いていた。SDSoCは、こうした「RTLが書けないエンジニア」にFPGAを使ってもらうための道具という位置づけになる(Photo04)。

具体的にはどんなフローになるか? といえば、まずC/C++を使って普通にシステムを作ることになる。次に実行しながらプロファイリングを行い、ボトルネックになっている部分をFPGA側に切り出して性能を評価、ある程度固まったところで完成という簡単なものだ(Photo05)。実はこの作業は非常に容易である。現在のバージョンでは、関数単位でそれを「H/Wで実施する」にチェックを入れるだけで、自動的に処理がLC側にオフロードされる形になる。

|

|

|

|

Photo05:もちろん、いきなり関数単位でFPGAにオフロードを掛けてから性能を見る、という乱暴な事も可能 |

Photo06:ちょっと判りにくいが、EclipseベースのIDE上で、ある関数を選んでそのプロパティの"Toggle HW/SW"という項目でHardwareを指定する「だけ」で自動的にFPGAが利用される |

もっとも実際には、「FPGAを使えば無条件で高速化できる」かどうかは必ずしも明らかではない。あるいは、高速化はされても十分ではない可能性もある。当たり前だがアプリケーションの主要な部分はCPU上で動作しており、特定の関数の部分だけRTL化され(これはSDSoCの内部からVivadoを呼び出して処理が行われる)る訳だが、実際にはそのRTLブロックに対して引数やデータを渡して処理を行い、結果をまた受けとる形になる。この受け渡しのメカニズムそのものも自動で生成されるが、それが必ずしも最適になるとは限らないからだ。そこでシステムレベルのProfilerを利用して、それぞれの負荷や利用率、あるいは利用するリソースなどを確認することが必要であり、これも併せて提供される形になる(Photo07)。加えていれば、この「受け渡す」「受け取る」には、そのために専用のコードが必要になる。従来だとこれを記述するのが大変だったのだが、SDSoCではこの部分が自動生成されるために手間要らず、というのも利点とされる。

実際にデモとして行われたのは、「Zynq 7020」を使った簡単なビデオフィルタリングアプリケーションである(Photo09)。これをソフトウェアで実装すると1fps出るか出ないかというあたりなのが、ある特定の関数のみFPGAにオフロードすることで、60fpsでフルに動くというモノだ。こちらはXilinx自身がビデオを公開しておりhttp://japan.xilinx.com/products/design-tools/sdx/sdsoc.htmlの「SDSoC開発環境のデモ(日本語字幕)」を見ていただくのが一番早いように思われる。ここでは1fps→60fpsで60倍ということになるが、そもそもHDMIが60fps以上で入出力できないから60倍でクランプされている可能性もあり、ルーチンの性能だけで言えばPhoto08の「最大100倍」も嘘ではないケースもあるだろう。