XilinxのUltraSCALEアーキテクチャFPGA

Hot Chips 26において、XilinxはUltraSCALEアーキテクチャと呼ぶ20nm世代のFPGAの技術についての発表を行った。

必要なバンド幅は増大し続けているので、Xilinxも、より高速のIOの開発を続けており、20nm世代のUltraSCALE FPGAでは、最大32.75Gb/で動作するIOを搭載している。また、最大120個と、高速で動作するIOの数を増やすことにも力を入れている。

そして、処理性能を向上させるためにはクロックの向上が必要になるが、クロック周波数を上げると相対的にクロックスキューが増えてしまいタイミングマージンが減ってしまうという問題がある。また、半導体の微細化で配線も細くなり、その結果、抵抗が増えてクロックの遅延やスキューが増えてしまうという問題が出てくる。

次の図の左側の絵のように、従来はチップの中心にクロックソースを置き、縦方向に32個のクロックバッファを置いてクロックを分配していたが、UltraSCALEアーキテクチャでは192~720個のクロックバッファを分散して配置し、どの位置にでもクロックソースを置くことができるようにした。そしてクロックドメインを細分化することでスキューを減少させている。

微細化で集積度が向上すると、配線もそれだけ多く必要になる。また、微細化で配線が細くなり抵抗が増えて遅延時間が長くなるという問題がある。これに対しては、ロジックブロックの密度の改善や、配置や配線の改善を行っているが、それだけでは不足で、配線層の追加を行っている。

特に、抵抗が大きくなる長い配線に対しては、厚み、幅ともに大きな上層の配線層を割り当ててR、Cを減らしている。

次の図は、LUTの使用率を横軸にとり、縦方向のマスの色で配線の困難さを表現している。黒は配線不能、緑は配線の混雑がない、その他は、色が明るくなるにつれて配線が容易になっていくといいう表現である。

図の左側の従来のFPGAではLUTの使用率が65%を超えると、黒の配線不能の領域が出てくるのに対して、配線層を増やした右側のUltraSCALEアーキテクチャでは、使用率が高くなると、配線が難しい領域が出てくるものの、混雑がひどくて配線不能というところまでは至っていない。この結果、タイミングクロージャまでの時間が短縮でき、最高動作周波数も1グレード向上できるという。

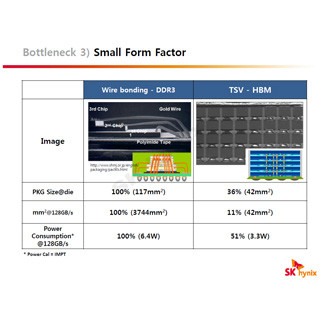

Xilinxは、1チップでは作れない巨大なFPGAは、複数のスライスをインタポーザで接続する2.5D実装で実現している。UltraSCALEアーキテクチャでも、同様な2.5D実装を使うが、スライス間に約2万本の配線領域を確保し、500MHz以上の動作を可能にするという。また、クロック分配もスライス間をつなぎ、スキューなどを抑えて単一チップに近い使い勝手を提供する。

消費電力は45nm/40nmプロセスのSpartan-6/Virtes-6から、28nmプロセスを使う7シリーズで最大で半減したが、20nm/16nmプロセスを使うUltraSCALEでは、さらに25%~45%の電力低減を目指している。スタティック電力の低減は、半導体プロセスの改善やチップの選別が中心となるが、その他の部分のアクティブな電力の低減には、これまでに説明した各種の技術が貢献している。

これまでに説明したことをまとめると、UltraSCALE FPGAでは、

- 最大120個のトランシーバを搭載し、最高速度も33Gb/sに引き上げて、IOバンド幅を改善

- 配線層の追加などで、配線を容易にし、性能を改善

- クロック分配の柔軟性と性能を改善

- 第2世代の2.5D実装で最大4.4Mロジックセルの巨大FPGAを実現

が新技術の目玉である。

今回のHot Chips 26においてAltera、Xilinxの両社が発表したFPGAは20nmプロセスの採用と回路技術によって、高密度、高性能化を行い、配線抵抗の増大や素子バラつきの増大などの微細化の問題を各種の技術でカバーしており、FPGAで実現できる機能の地平線を拡大している。まだまだ、FPGAの進化は続きそうである。